Question: Computer Architecture question please solve the above question. If you need any info let me know what info you need. A-42Appendix A Instruction Set Principles

Computer Architecture question

please solve the above question.

If you need any info let me know what info you need.

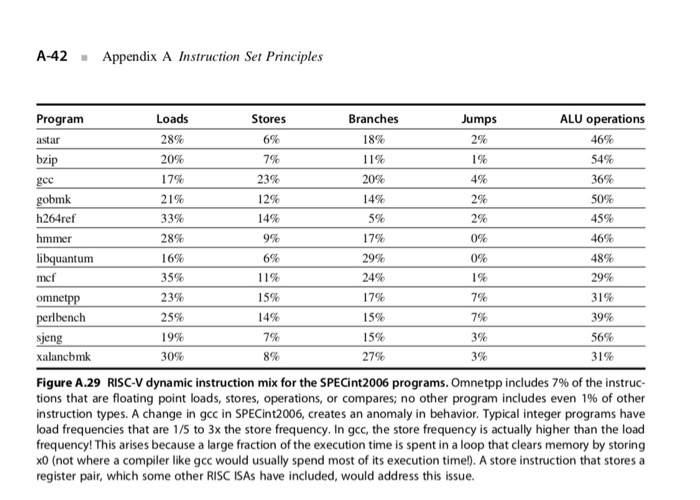

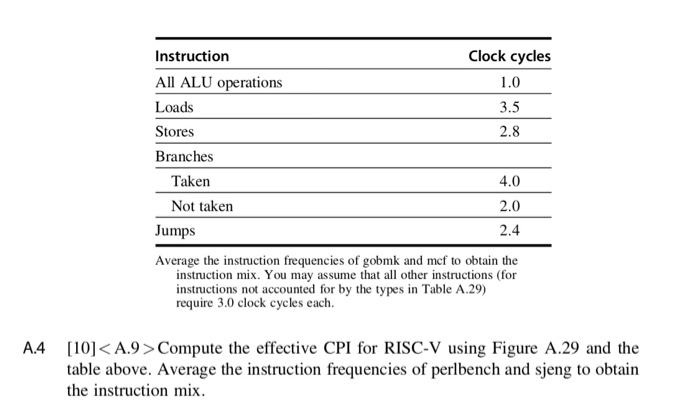

A-42Appendix A Instruction Set Principles Program astar bzi Stores Branches 18% 11% 20% 14% 5% 17% 29% 24% 17% I 5% 1 5% 27% Jumps ALU operations 28% 20% 17% 7% 23% 12% 14% 54% 36% 50% 45% 1% 4% obmk h264ref hmmer 33% 28% 16% 35% 23% 25% 19% 2% 0% 48% 29% 31% tum 11% 1% 7% 7% 3% 3% mC 15% rlbench 7% 56% 31% xalancbmk 8% Figure A.29 RISC-V dynamic instruction mix for the SPECi nt2006 programs. Omnetpp includes 7% of the instruc tions that are floating point loads, stores, operations, or compares; no other program includes even 1% of other instruction types. A change in gcc in SPECint2006, creates an anomaly in behavior. Typical integer programs have load frequencies that are 1/5 to 3x the store frequency. In gcc, the store frequency is actually higher than the load frequency! This arises because a large fraction of the execution time is spent in a loop that clears memory by storing x0 (not where a compiler like gcc would usually spend most of its execution time!). A store instruction that storesa register pair, which some other RISC ISAs have included, would address this issue Clock cycles Instruction All ALU operations Loads Stores Branches 3.5 2.8 4.0 2.0 2.4 and mcf to obtain the instruction mix. You may assume that all other instructions (for Taken Not taken Jumps Average the instruction frequencies of gobmk instructions not accounted for by the types in Table A.29) require 3.0 clock cycles each A.4 [10] Compute the effective CPI for RISC-V using Figure A.29 and the table above. Average the instruction frequencies of perlbench and sjeng to obtain the instruction mix

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts