Question: Computer architecture The following code fragment is executed using classic five-stage pipeline MIPS Architecture. The branches are resolved in EX stage and no branch prediction

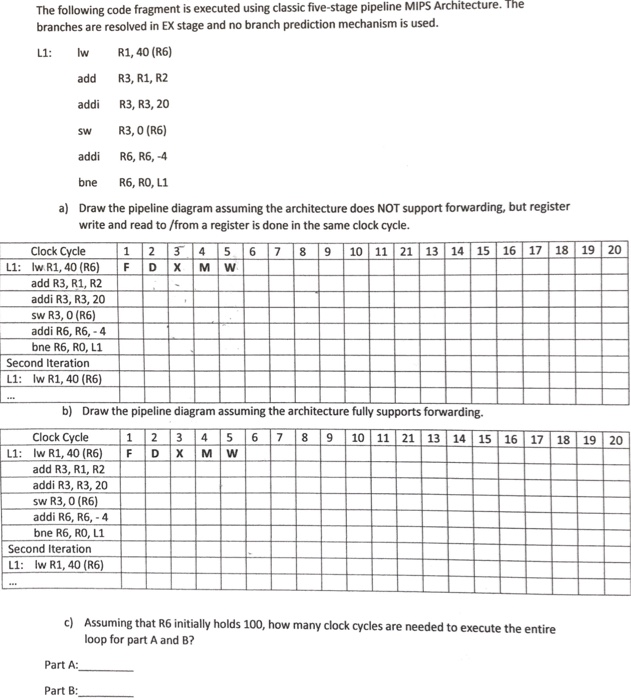

The following code fragment is executed using classic five-stage pipeline MIPS Architecture. The branches are resolved in EX stage and no branch prediction mechanism is used. lw R1,40 (R6) add R3, R1, R2 addi R3, R3, 20 s R3, 0 (R6) addi R6, R6,-4 bne R6, RO, L1 Draw the pipeline diagram assuming the architecture does NOT support forwarding, but register L1: a) write and read to /from a register is done in the same clock cycle Clock C 1 2 3 4 5 6 7 8 9 10 11 2113 1415 16 17 18 19 20 add R3, R1, R2 addi R3, R3, 20 Sw R3, O (R6) addi R6, R6,-4 bne R6, RO, L1 Second Iteration L1: Iw R1, 40 (R6) b) Draw the pipeline diagram assuming the architecture fully supports forwarding. Clock 1 2 3 4 5 6 7 8 910 11 21 13 14 15 16 17 18 19 20 add R3, R1, R2 addi R3, R3, 20 addi R6, R6,-4 bne R6, RO, L1 Second Iteration L1: lw R1, 40 (R6 Assuming that R6 initially holds 100, how many clock cycles are needed to execute the entire loop for part A and B? c) Part A: Part B

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts