Question: Computer Organization and Architecture : Suppose we want an error-correcting code that will allow all single-bit errors to be corrected for memory words of length

Computer Organization and Architecture :

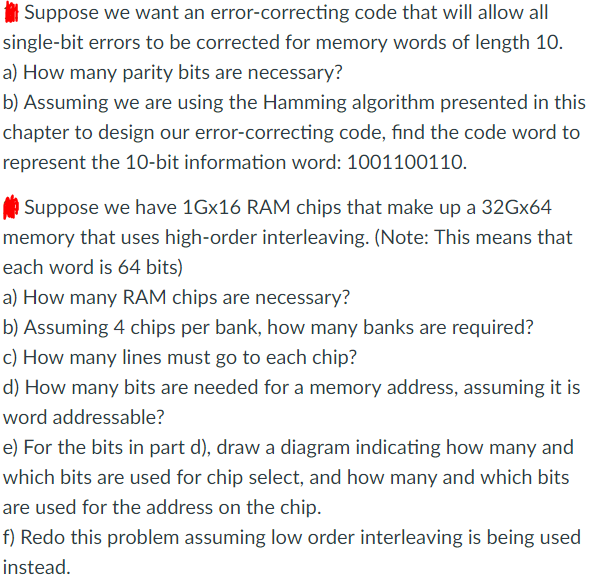

Suppose we want an error-correcting code that will allow all single-bit errors to be corrected for memory words of length 10. a) How many parity bits are necessary? b) Assuming we are using the Hamming algorithm presented in this chapter to design our error-correcting code, find the code word to represent the 10-bit information word: 1001100110. Suppose we have 1Gx16 RAM chips that make up a 32Gx64 memory that uses high-order interleaving. (Note: This means that each word is 64 bits) a) How many RAM chips are necessary? b) Assuming 4 chips per bank, how many banks are required? c) How many lines must go to each chip? d) How many bits are needed for a memory address, assuming it is word addressable e) For the bits in part d), draw a diagram indicating how many and which bits are used for chip select, and how many and which bits are used for the address on the chip. f) Redo this problem assuming low order interleaving is being used instead

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts