Question: Computer organization and design, mips instructions, please solve fast I will upvote for you Computer organization and design, mips instructions, please solve fast I will

Computer organization and design, mips instructions, please solve fast I will upvote for you

Computer organization and design, mips instructions, please solve fast I will upvote for you

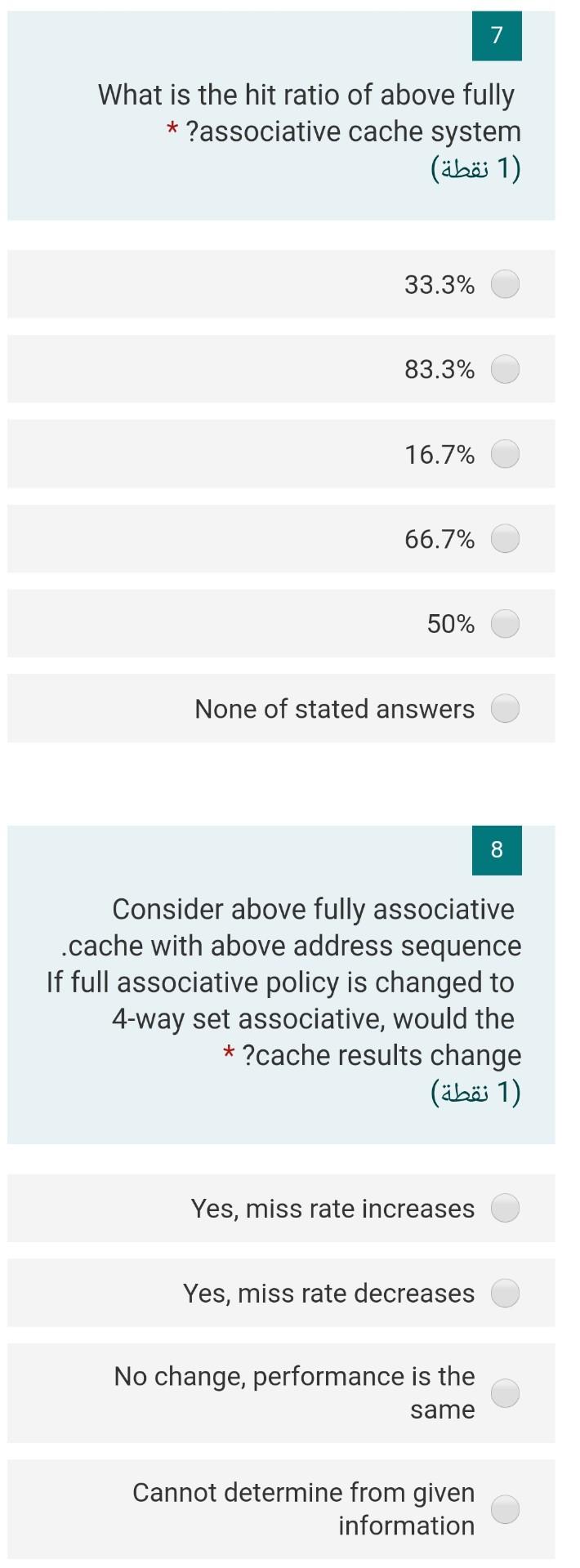

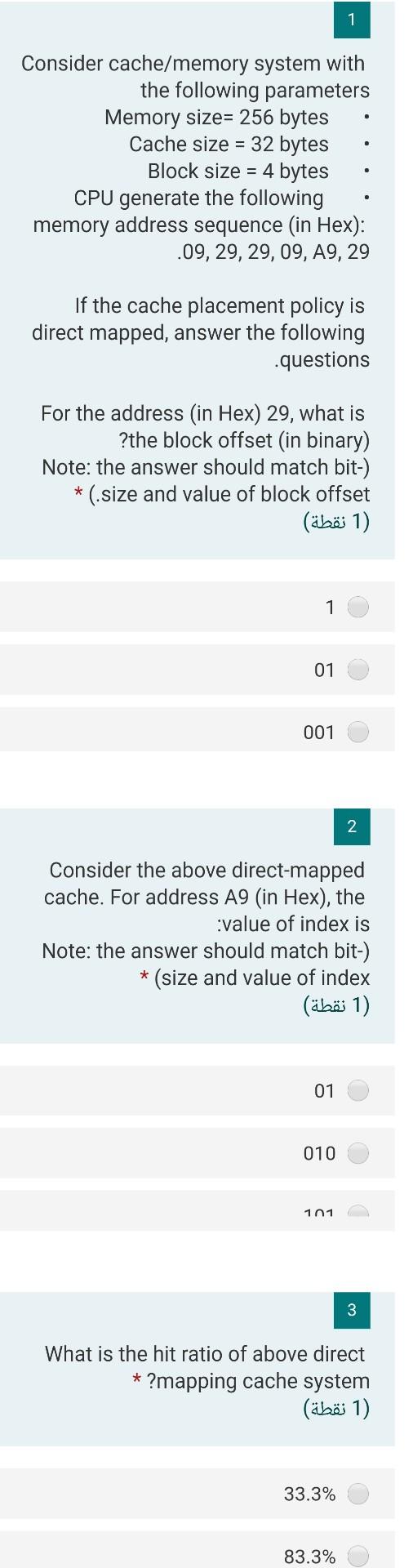

7 What is the hit ratio of above fully * ?associative cache system 1) (1 ) 33.3% 83.3% 16.7% 66.7% 50% None of stated answers 8 Consider above fully associative .cache with above address sequence If full associative policy is changed to 4-way set associative, would the * ?cache results change (1) (1 ) Yes, miss rate increases Yes, miss rate decreases No change, performance is the same Cannot determine from given information 1 Consider cache/memory system with the following parameters Memory size= 256 bytes Cache size = 32 bytes Block size = 4 bytes CPU generate the following memory address sequence (in Hex): .09, 29, 29, 09, A9, 29 If the cache placement policy is direct mapped, answer the following .questions For the address in Hex) 29, what is ?the block offset (in binary) Note: the answer should match bit-) * (.size and value of block offset (b 1) 1 01 001 2 Consider the above direct-mapped cache. For address A9 (in Hex), the value of index is Note: the answer should match bit-) (size and value of index (b 1) * 01 010 101 3 What is the hit ratio of above direct * ?mapping cache system 1) (1 ) 33.3% 83.3% 7 What is the hit ratio of above fully * ?associative cache system 1) (1 ) 33.3% 83.3% 16.7% 66.7% 50% None of stated answers 8 Consider above fully associative .cache with above address sequence If full associative policy is changed to 4-way set associative, would the * ?cache results change (1) (1 ) Yes, miss rate increases Yes, miss rate decreases No change, performance is the same Cannot determine from given information 1 Consider cache/memory system with the following parameters Memory size= 256 bytes Cache size = 32 bytes Block size = 4 bytes CPU generate the following memory address sequence (in Hex): .09, 29, 29, 09, A9, 29 If the cache placement policy is direct mapped, answer the following .questions For the address in Hex) 29, what is ?the block offset (in binary) Note: the answer should match bit-) * (.size and value of block offset (b 1) 1 01 001 2 Consider the above direct-mapped cache. For address A9 (in Hex), the value of index is Note: the answer should match bit-) (size and value of index (b 1) * 01 010 101 3 What is the hit ratio of above direct * ?mapping cache system 1) (1 ) 33.3% 83.3%

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts