Question: Computer Science - Java Background: When we start to build a logic simulation, we will need to describe the system of logic gates (a logic

Computer Science - Java

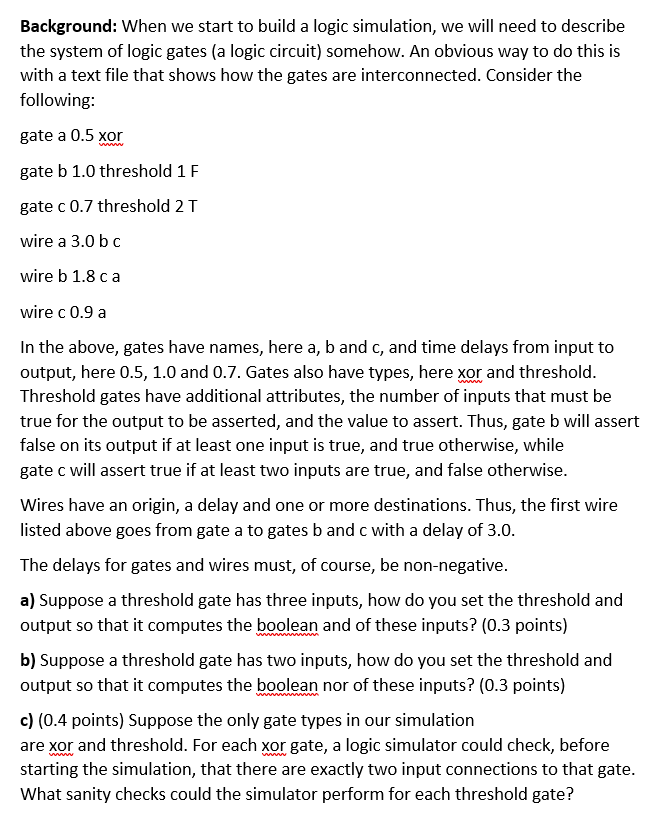

Background: When we start to build a logic simulation, we will need to describe the system of logic gates (a logic circuit) somehow. An obvious way to do this is with a text file that shows how the gates are interconnected. Consider the following gate a 0.5 xor gate b 1.0 threshold 1F gate c 0.7 threshold 2 T wire a 3.0 b c wire b 1.8 ca wire c 0.9 a In the above, gates have names, here a, b and c, and time delays from input t output, here 0.5, 1.0 and 0.7. Gates also have types, here xor and threshold. Threshold gates have additional attributes, the number of inputs that must be true for the output to be asserted, and the value to assert. Thus, gate b will assert false on its output if at least one input is true, and true otherwise, while gate c willassert true if at least two inputs are true, and false otherwise. Wires have an origin, a delay and one or more destinations. Thus, the first wire listed above goes from gate a to gates b and c with a delay of The delays for gates and wires must, of course, be non-negative. a) Suppose a threshold gate has three inputs, how do you set the threshold and output so that it computes the boolean and of these inputs? (0.3 points) b) Suppose a threshold gate has two inputs, how do you set the threshold and output so that it computes the boolean nor of these inputs? (0.3 points) c) (0.4 points) Suppose the only gate types in our simulation are xor and threshold. For each xor gate, a logic simulator could check, before starting the simulation, that there are exactly two input connections to that gate What sanity checks could the simulator perform for each threshold gate? Background: When we start to build a logic simulation, we will need to describe the system of logic gates (a logic circuit) somehow. An obvious way to do this is with a text file that shows how the gates are interconnected. Consider the following gate a 0.5 xor gate b 1.0 threshold 1F gate c 0.7 threshold 2 T wire a 3.0 b c wire b 1.8 ca wire c 0.9 a In the above, gates have names, here a, b and c, and time delays from input t output, here 0.5, 1.0 and 0.7. Gates also have types, here xor and threshold. Threshold gates have additional attributes, the number of inputs that must be true for the output to be asserted, and the value to assert. Thus, gate b will assert false on its output if at least one input is true, and true otherwise, while gate c willassert true if at least two inputs are true, and false otherwise. Wires have an origin, a delay and one or more destinations. Thus, the first wire listed above goes from gate a to gates b and c with a delay of The delays for gates and wires must, of course, be non-negative. a) Suppose a threshold gate has three inputs, how do you set the threshold and output so that it computes the boolean and of these inputs? (0.3 points) b) Suppose a threshold gate has two inputs, how do you set the threshold and output so that it computes the boolean nor of these inputs? (0.3 points) c) (0.4 points) Suppose the only gate types in our simulation are xor and threshold. For each xor gate, a logic simulator could check, before starting the simulation, that there are exactly two input connections to that gate What sanity checks could the simulator perform for each threshold gate

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts