Question: Consider an Acc - ISA CPU that executes the pseudo - code shown. Do the following: . . . / / some code while {

Consider an AccISA CPU that executes the pseudocode shown. Do the following:

some code

while trueloop forever

TABC; where stands for bitwise XOR

some other code not given

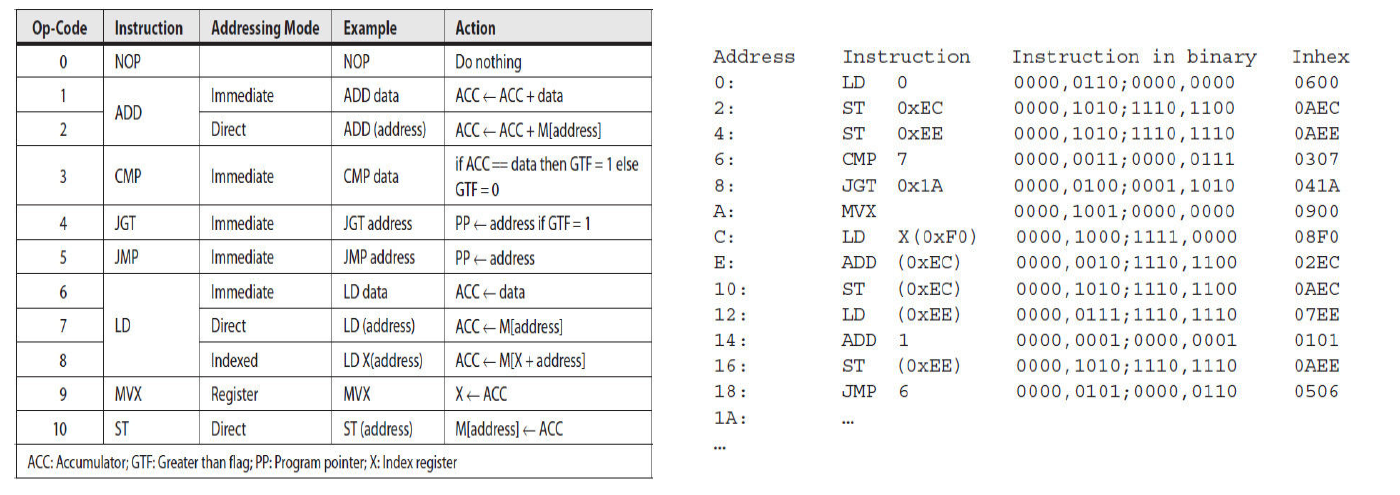

a Create a set of bit AccISA instructions with bit opcodes and bit operands. Any of the variables A through C may be a negative s complement number.

b Write an assembly program using your instruction set. Also assume that the code starts from memory address and increases by and data starts from memory address xF and decreases by

c Manually assemble your assembly program and write instructions in binary and in hex. Assign opcodes to the instructions in the order they were used in the assembly program, starting from address

Hints and Guidelines:

Refer to the attached table as an example for question a

From the above pseudocode, identify what operations you need to perform. How about ADD, SUB, XOR, etc? For each of these codes assign a bit opcode. You need opcodes and hence you are good with bits.

Keep in mind that you can manipulate the ACC, by accessing the operands from memory directly. There are several examples in the book in this regard.

For question a

A table with bit OPCODEs Instructions and Actions be listed.

Example:

XOR address

Assign addresses LD SUB, ADD, XOR, ST BR in that order starting with opcode

For question b

You have several examples of code segments and data segments.

Start code section address from ; Per se for all the instruction flow

For the data segment it will be byte of data, and hence all the data variables get stored in the memory with

i Example:

XF T RB

ii Order the variables T A B C in this order.

For question c you may refer to the assembly code in the provided photo. Note the two columns: Instruction in binary and in Hex.tableOpCode,Instruction,Addressing Mode,Example,ActionNOP,,NOP,Do nothingADD,Immediate,ADD data,ACClarrACC dataDirect,ADD addressACClarrACCM address CMPImmediate,CMP data,tableif ACC data then GTF elseGTFJGTImmediate,JGT address,PPlarr address if GTFJMPImmediate,JMP address,PPlarr addressLDImmediate,LD data,ACClarr dataDirect,LD addressACClarr MaddressIndexed,LDXaddressACClarrMx address MVxRegister,MVXxlarrACCSTDirect,ST addressMaddress larr ACC

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock