Question: Consider the 5 - stage pipelined processor shown in Figure 1 . Let us assume that branch instructions are determined in MEM stage ( i

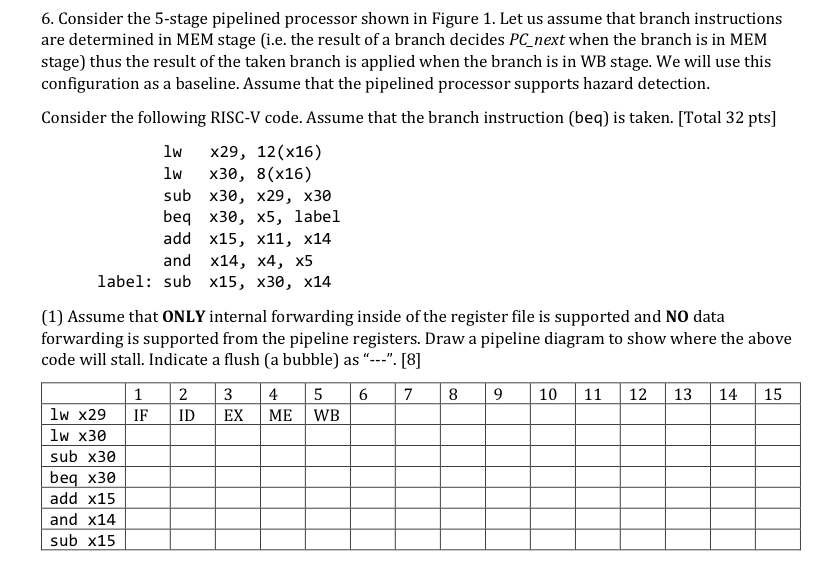

Consider the stage pipelined processor shown in Figure Let us assume that branch instructions are determined in MEM stage ie the result of a branch decides PCnext when the branch is in MEM stage thus the result of the taken branch is applied when the branch is in WB stage. We will use this configuration as a baseline. Assume that the pipelined processor supports hazard detection.

Consider the following RISCV code. Assume that the branch instruction beq is taken. Total pts Assume that ONLY internal forwarding inside of the register file is supported and NO data forwarding is supported from the pipeline registers. Draw a pipeline diagram to show where the above code will stall. Indicate a flush a bubble as

tableIw IFIDEXMEWBlw sub beq add and sub

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock