Question: Consider the basic MIPS pipeline (that is, without any structural hazards but also without any optimizations). Consider also the following assembly code segment. addi

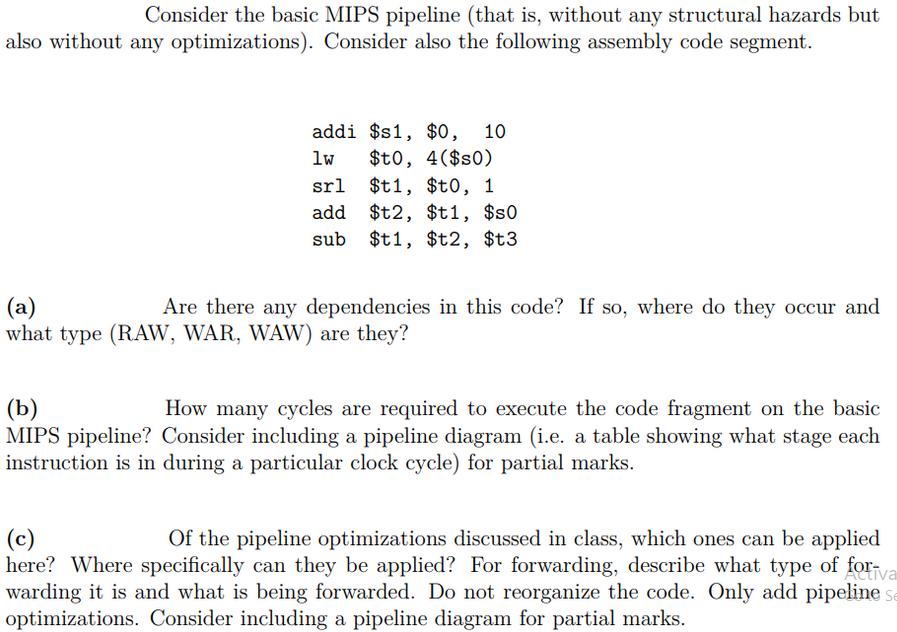

Consider the basic MIPS pipeline (that is, without any structural hazards but also without any optimizations). Consider also the following assembly code segment. addi $s1, $0, lw $t0, 4($s0) srl $t1, $t0, 1 add $t2, $t1, $s0 sub $t1, $t2, $t3 (a) Are there any dependencies in this code? If so, where do they occur and what type (RAW, WAR, WAW) are they? (b) How many cycles are required to execute the code fragment on the basic MIPS pipeline? Consider including a pipeline diagram (i.e. a table showing what stage each instruction is in during a particular clock cycle) for partial marks. (c) Activa Of the pipeline optimizations discussed in class, which ones can be applied here? Where specifically can they be applied? For forwarding, describe what type of for- warding it is and what is being forwarded. Do not reorganize the code. Only add pipeline se optimizations. Consider including a pipeline diagram for partial marks.

Step by Step Solution

There are 3 Steps involved in it

a Dependencies in the code 1 RAW ReadAfterWrite dependency between lw t0 4s0 and srl t1 t0 1 2 RAW d... View full answer

Get step-by-step solutions from verified subject matter experts