Question: Consider the following ARM assembly program. The first column corresponds to the address (in decimal) where each data/instruction is stored in memory. The second column

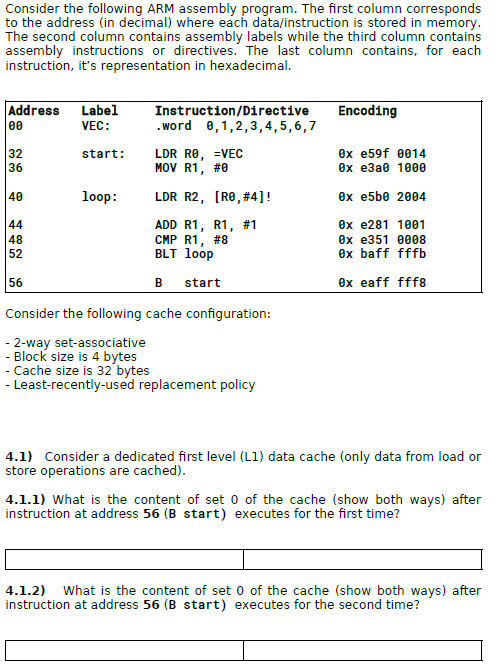

Consider the following ARM assembly program. The first column corresponds to the address (in decimal) where each data/instruction is stored in memory. The second column contains assembly labels while the third column contains assembly instructions or directives. The last column contains, for each instruction, it's representation in hexadecimal.

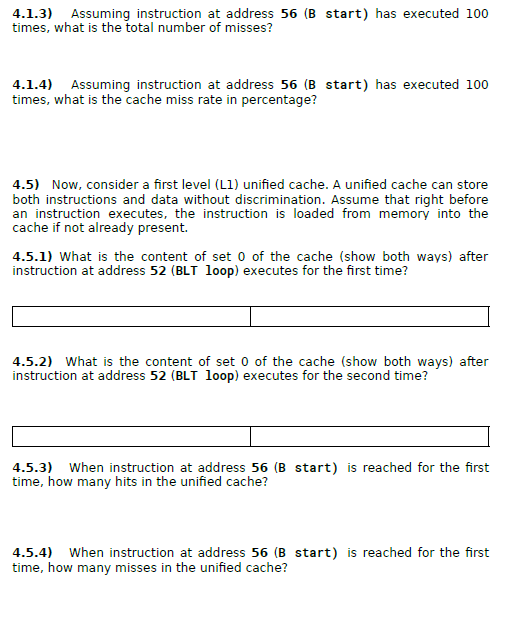

Consider the following ARM assembly program. The first column corresponds to the address (in decimal) where each data/instruction is stored in memory. The second column contains assembly labels while the third column contains assembly instructions or directives. The last column contains, for each instruction, it's representation in hexadecimal. Address Label VEC: Instruction/Directive word 6,1,2,3,4,5,6,7 Encoding start: LDR RO, VEC MOV R1, #0 ex e59f 2014 ex e3ae 1000 loop: LDR R2, [RO, #4]: ex e5be 2004 ADD R1, R1, #1 CMP R1, #8 BLT loop ex e281 1001 Ox e351 0008 ex baff fffb B start ex eaff fff8 Consider the following cache configuration: - 2-way set-associative - Block size is 4 bytes - Cache size is 32 bytes - Least-recently-used replacement policy 4.1) Consider a dedicated first level (L1) data cache (only data from load or store operations are cached). 4.1.1) What is the content of set 0 of the cache (show both ways) after instruction at address 56 (B start) executes for the first time? 4.1.2) What is the content of set 0 of the cache (show both ways) after instruction at address 56 (B start) executes for the second time? 4.1.3) Assuming instruction at address 56 (B start) has executed 100 times, what is the total number of misses? 4.1.4) Assuming instruction at address 56 (B start) has executed 100 times, what is the cache miss rate in percentage? 4.5) Now, consider a first level (L1) unified cache. A unified cache can store both instructions and data without discrimination. Assume that right before an instruction executes, the instruction is loaded from memory into the cache if not already present. 4.5.1) What is the content of set 0 of the cache (show both ways) after instruction at address 52 (BLT loop) executes for the first time? 4.5.2) What is the content of set 0 of the cache (show both ways) after instruction at address 52 (BLT loop) executes for the second time? 4.5.3) When instruction at address 56 (B start) is reached for the first time, how many hits in the unified cache? 4.5.4) When instruction at address 56 (B start) is reached for the first time, how many misses in the unified cache? Consider the following ARM assembly program. The first column corresponds to the address (in decimal) where each data/instruction is stored in memory. The second column contains assembly labels while the third column contains assembly instructions or directives. The last column contains, for each instruction, it's representation in hexadecimal. Address Label VEC: Instruction/Directive word 6,1,2,3,4,5,6,7 Encoding start: LDR RO, VEC MOV R1, #0 ex e59f 2014 ex e3ae 1000 loop: LDR R2, [RO, #4]: ex e5be 2004 ADD R1, R1, #1 CMP R1, #8 BLT loop ex e281 1001 Ox e351 0008 ex baff fffb B start ex eaff fff8 Consider the following cache configuration: - 2-way set-associative - Block size is 4 bytes - Cache size is 32 bytes - Least-recently-used replacement policy 4.1) Consider a dedicated first level (L1) data cache (only data from load or store operations are cached). 4.1.1) What is the content of set 0 of the cache (show both ways) after instruction at address 56 (B start) executes for the first time? 4.1.2) What is the content of set 0 of the cache (show both ways) after instruction at address 56 (B start) executes for the second time? 4.1.3) Assuming instruction at address 56 (B start) has executed 100 times, what is the total number of misses? 4.1.4) Assuming instruction at address 56 (B start) has executed 100 times, what is the cache miss rate in percentage? 4.5) Now, consider a first level (L1) unified cache. A unified cache can store both instructions and data without discrimination. Assume that right before an instruction executes, the instruction is loaded from memory into the cache if not already present. 4.5.1) What is the content of set 0 of the cache (show both ways) after instruction at address 52 (BLT loop) executes for the first time? 4.5.2) What is the content of set 0 of the cache (show both ways) after instruction at address 52 (BLT loop) executes for the second time? 4.5.3) When instruction at address 56 (B start) is reached for the first time, how many hits in the unified cache? 4.5.4) When instruction at address 56 (B start) is reached for the first time, how many misses in the unified cache

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts