Question: Consider the following assembly language program that runs on an AVR micro - architecture with a 5 stage pipeline and a hazard unit that uses

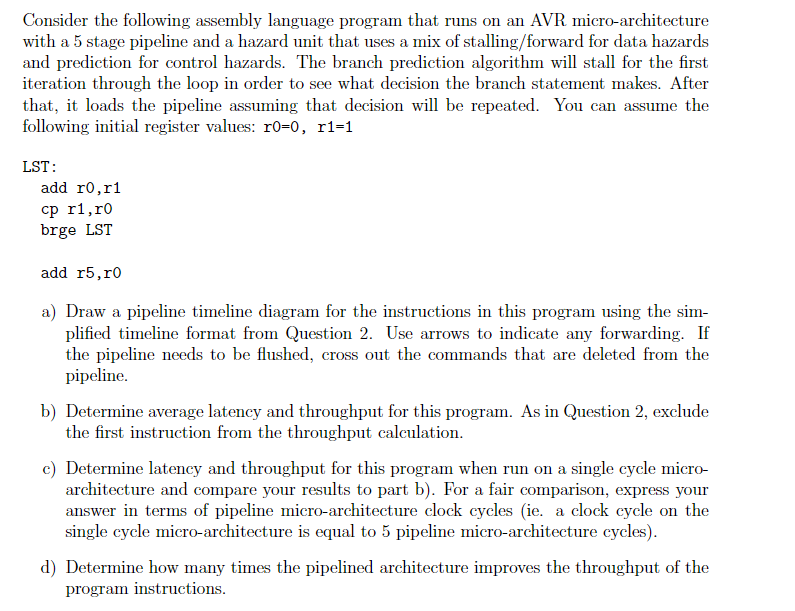

Consider the following assembly language program that runs on an AVR microarchitecture

with a stage pipeline and a hazard unit that uses a mix of stallingforward for data hazards

and prediction for control hazards. The branch prediction algorithm will stall for the first

iteration through the loop in order to see what decision the branch statement makes. After

that, it loads the pipeline assuming that decision will be repeated. You can assume the

following initial register values:

LST :

add

cp rr

brge LST

add

a Draw a pipeline timeline diagram for the instructions in this program using the sim

plified timeline format from Question Use arrows to indicate any forwarding. If

the pipeline needs to be flushed, cross out the commands that are deleted from the

pipeline.

b Determine average latency and throughput for this program. As in Question exclude

the first instruction from the throughput calculation.

c Determine latency and throughput for this program when run on a single cycle micro

architecture and compare your results to part b For a fair comparison, express your

answer in terms of pipeline microarchitecture clock cycles ie a clock cycle on the

single cycle microarchitecture is equal to pipeline microarchitecture cycles

d Determine how many times the pipelined architecture improves the throughput of the

program instructions.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock