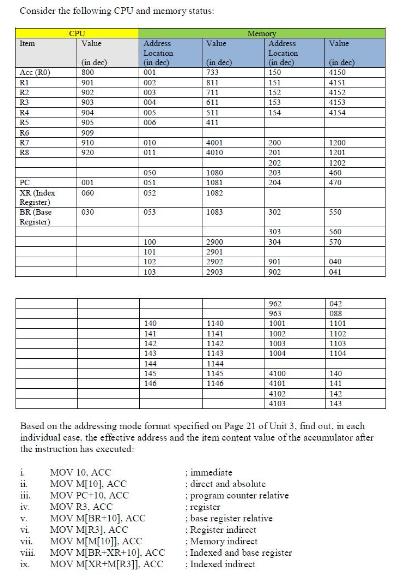

Question: Consider the following CPU and memory status: CPU Memory Item Value Address Value Address Value Location Location (in dec) (in dec) (in dec) (in

Consider the following CPU and memory status: CPU Memory Item Value Address Value Address Value Location Location (in dec) (in dec) (in dec) (in dec) (in dec) Acc (RO) 900 001 733 150 4150 RI 901 003 811 151 4151 R2 902 003 711 152 4152 R3 903 004 611 153 4153 R4 904 005 511 154 4154 RS 905 006 411 R6 909 R7 510 010 4001 200 1200 RS 920 011 4010 201 1201 202 1202 050 1080 203 450 PC 001 051 1081 204 470 XR (Index 060 052 1082 Register) BR (Base 030 053 1083 302 550 Register) 303 560 100 2900 304 570 101 2901 102 2902 901 040 103 2903 902 041 962 042 963 088 140 1140 1001 1101 1411 1141 1002 1102 142 1142 1003 1103 1431 1143 1004 1104 144 1144 145 1145 4100 1401 1461 1146 41011 141 4102 143 4103 143) Based on the addressing mode format specified on Page 21 of Unit 3. find out. in each individual case, the effective address and the item content value of the accumulator after the instruction has executed: i MOV 10. ACC ii. MOV M[10]. ACC iii. MOV PC+10, ACC iv. MOV R3. ACC V MOV M[BR-10], ACC vi MOV MIR3]. ACC vii. MOV M[M[10]]. ACC viii. MOV M[BR-XR+10]. ACC ix. MOV M[XR+M[R3]], ACC ; immediate : direct and absolute program counter relative :register ; base register relative Register indirect Memory indirect Indexed and base register :Indexed indirect

Step by Step Solution

3.47 Rating (154 Votes )

There are 3 Steps involved in it

Lets analyze each instruction based on the addressing mode format specified on Page 21 of Unit 3 MOV 10 ACC Immediate Addressing Effective Address The ... View full answer

Get step-by-step solutions from verified subject matter experts