Consider the following fragment of the Data Flow Graph (DFG) of the differential equation solver used...

Fantastic news! We've Found the answer you've been seeking!

Question:

Transcribed Image Text:

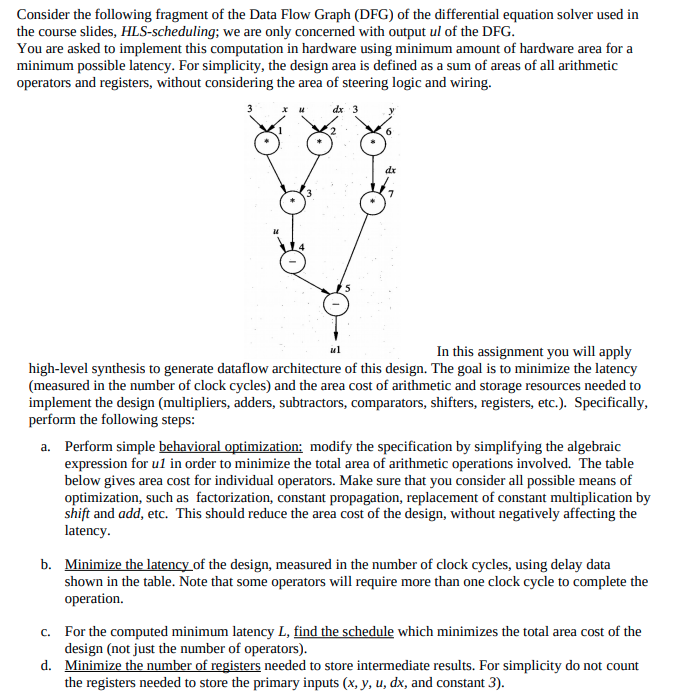

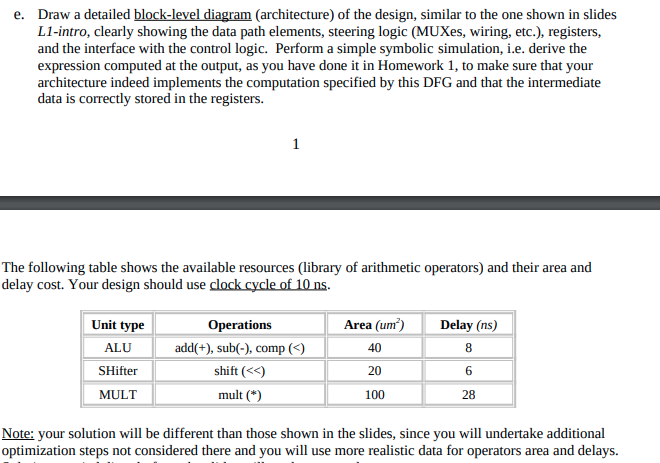

Consider the following fragment of the Data Flow Graph (DFG) of the differential equation solver used in the course slides, HLS-scheduling; we are only concerned with output ul of the DFG. You are asked to implement this computation in hardware using minimum amount of hardware area for a minimum possible latency. For simplicity, the design area is defined as a sum of areas of all arithmetic operators and registers, without considering the area of steering logic and wiring. dx 3 dx ul In this assignment you will apply high-level synthesis to generate dataflow architecture of this design. The goal is to minimize the latency (measured in the number of clock cycles) and the area cost of arithmetic and storage resources needed to implement the design (multipliers, adders, subtractors, comparators, shifters, registers, etc.). Specifically, perform the following steps: a. Perform simple behavioral optimization: modify the specification by simplifying the algebraic expression for u1 in order to minimize the total area of arithmetic operations involved. The table below gives area cost for individual operators. Make sure that you consider all possible means of optimization, such as factorization, constant propagation, replacement of constant multiplication by shift and add, etc. This should reduce the area cost of the design, without negatively affecting the latency. b. Minimize the latency of the design, measured in the number of clock cycles, using delay data shown in the table. Note that some operators will require more than one clock cycle to complete the operation. c. For the computed minimum latency L, find the schedule which minimizes the total area cost of the design (not just the number of operators). d. Minimize the number of registers needed to store intermediate results. For simplicity do not count the registers needed to store the primary inputs (x, y, u, dx, and constant 3). e. Draw a detailed block-level diagram (architecture) of the design, similar to the one shown in slides L1-intro, clearly showing the data path elements, steering logic (MUXes, wiring, etc.), registers, and the interface with the control logic. Perform a simple symbolic simulation, i.e. derive the expression computed at the output, as you have done it in Homework 1, to make sure that your architecture indeed implements the computation specified by this DFG and that the intermediate data is correctly stored in the registers. The following table shows the available resources (library of arithmetic operators) and their area and delay cost. Your design should use clock cycle of 10 ns. Unit type ALU SHifter MULT Operations add(+), sub(-), comp ( Consider the following fragment of the Data Flow Graph (DFG) of the differential equation solver used in the course slides, HLS-scheduling; we are only concerned with output ul of the DFG. You are asked to implement this computation in hardware using minimum amount of hardware area for a minimum possible latency. For simplicity, the design area is defined as a sum of areas of all arithmetic operators and registers, without considering the area of steering logic and wiring. dx 3 dx ul In this assignment you will apply high-level synthesis to generate dataflow architecture of this design. The goal is to minimize the latency (measured in the number of clock cycles) and the area cost of arithmetic and storage resources needed to implement the design (multipliers, adders, subtractors, comparators, shifters, registers, etc.). Specifically, perform the following steps: a. Perform simple behavioral optimization: modify the specification by simplifying the algebraic expression for u1 in order to minimize the total area of arithmetic operations involved. The table below gives area cost for individual operators. Make sure that you consider all possible means of optimization, such as factorization, constant propagation, replacement of constant multiplication by shift and add, etc. This should reduce the area cost of the design, without negatively affecting the latency. b. Minimize the latency of the design, measured in the number of clock cycles, using delay data shown in the table. Note that some operators will require more than one clock cycle to complete the operation. c. For the computed minimum latency L, find the schedule which minimizes the total area cost of the design (not just the number of operators). d. Minimize the number of registers needed to store intermediate results. For simplicity do not count the registers needed to store the primary inputs (x, y, u, dx, and constant 3). e. Draw a detailed block-level diagram (architecture) of the design, similar to the one shown in slides L1-intro, clearly showing the data path elements, steering logic (MUXes, wiring, etc.), registers, and the interface with the control logic. Perform a simple symbolic simulation, i.e. derive the expression computed at the output, as you have done it in Homework 1, to make sure that your architecture indeed implements the computation specified by this DFG and that the intermediate data is correctly stored in the registers. The following table shows the available resources (library of arithmetic operators) and their area and delay cost. Your design should use clock cycle of 10 ns. Unit type ALU SHifter MULT Operations add(+), sub(-), comp (

Expert Answer:

Answer rating: 100% (QA)

implement a computation in hardware using highlevel synthesis with the goals of minimizing latency a... View the full answer

Related Book For

Management Accounting Information for Decision-Making and Strategy Execution

ISBN: 978-0137024971

6th Edition

Authors: Anthony A. Atkinson, Robert S. Kaplan, Ella Mae Matsumura, S. Mark Young

Posted Date:

Students also viewed these programming questions

-

Ordinary Simple Annuities & Ordinary General Annuities 16. A loan of $40000.00 is to be repaid by equal quarterly payments for 5 years. What is the size of each quarterly payment if the interest is...

-

In this exercise, we examine how resource hazards, control hazards, and Instruction Set Architecture (ISA) design can affect pipelined execution. Problems in this exercise refer to the following...

-

Planning is one of the most important management functions in any business. A front office managers first step in planning should involve determine the departments goals. Planning also includes...

-

The formula F(x) = 3x + C gives a different function for each value of C. All of these functions, however, have the same derivative with respect to x, namely F(x) = 3. Are these the only...

-

Ted and Mary are playing a game of catch in frame S", which is moving at 0.600c with respect to frame S, while Jim, at rest in frame S watches the action (Fig. P39.59). Ted throws the ball to Mary at...

-

Ionization energy is the minimum energy required to remove an electron from an atom. It is usually expressed in units of kJ/mol, that is, the energy in kilojoules required to remove one mole of...

-

What is the minimum horsepower for trending to extend the life of the machine if its noncritical?

-

Cottonwood Company reports the following operating results for the month of April. Management is considering the following course of action to increase net income: Reduce the selling price by 10%,...

-

You have been hired as a new accountant for Bake-Me-Some-Bread, Inc. They have asked you to calculate the company's Manufacturing Overhead Rate. You are given the following data from the accounting...

-

Acme Manufacturing makes a variety of household appliances at a single manufacturing facility. The expected demand for one of these appliances during the next four months is shown in the following...

-

You are a graduate of York College, CUNY, and an employee of one of the Big 4 accounting firms. You are a member of a team assigned to Ultra Cable Company to access two shareholders concerns: 1 . The...

-

In Earth science, which of the following describes the fundamental difference between weathering and erosion? A)Weathering involves the physical breakdown of rocks, while erosion involves the removal...

-

Based on your experience, share an example of a Transformational, Servant or an Authentic Leaders. Describe the characteristics the person displays that represent that style. How do you think the...

-

You could use a wheelbarrow on a ramp to load your surplus 10kg of hamsters into the waiting train car that is 2m above the ground. The force needed to push the wheelbarrow up the ramp is 20N and the...

-

Work throughthe case using just ONE of the following models of your choice to reach and justify a responsible and ethical judgment in relation to the case study: ...

-

When is impersonal communication harmful?when might impersonal communication desire? Explain this phrase "one cannot not communicate

-

it Calculate the thresold kinetic energy for the reaction p+ H 7H + H a) of protons are incident on 3H at jest. be of it le tritons are incident on proton.

-

Flicker, Inc., a closely held corporation, acquired a passive activity this year. Gross income from operations of the activity was $160,000. Operating expenses, not including depreciation, were...

-

1. What does a capital spending plan do? 2. What is an example of a capacity-related expenditure?

-

What is a stock option plan?

-

Gurland Valves Company manufactures brass valves that meet precise specification standards. All finished valves are inspected before being packaged and shipped to customers. Rejected valves are...

-

Is an oscillating object in translational equilibrium?

-

How far above Farth's surface must a \(10,000-\mathrm{kg}\) boulder be moved to increase the mass of the Earthboulder system by \(2.50 \mathrm{mg}\) ? Assume the same ratio of energy change to mass...

-

Show that for small displacements the restoring force exerted on part 2 of the displaced string in Figure 15.14 is linearly proportional to the displacement of that part from its equilibrium...

Study smarter with the SolutionInn App