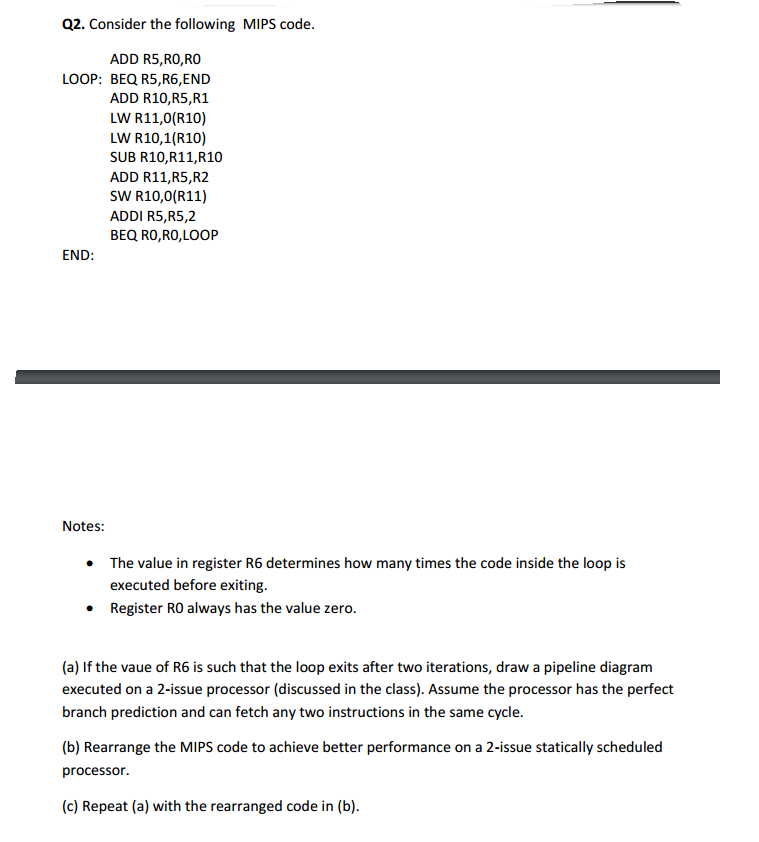

Question: Consider the following MIPS code. ADD R5, R0, R0 LOOP: BEQ R5, R6, END ADD R10, R5, R1 LW R11, 0(R10) LW R10, 1(R10) SUB

Consider the following MIPS code. ADD R5, R0, R0 LOOP: BEQ R5, R6, END ADD R10, R5, R1 LW R11, 0(R10) LW R10, 1(R10) SUB R10, R11, R10 ADD R11, R5, R2 SW R10, 0(R11) ADDI R5, R5, 2 BEQ RO, RO, LOOP END: (a) If the value of R6 is such that the loop exits after two iterations, draw a pipeline diagram executed on a 2-issue processor (discussed in the class). Assume the processor has the perfect branch prediction and can fetch any two instructions in the same cycle. (b) Rearrange the MIPS code to achieve better performance on a 2-issue statically scheduled processor. (c) Repeat (a) with the rearranged code in (b)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts