Question: Consider the previous assembly program. L . D F 0 1 0 ( R 1 ) L . D F 1 2 0 ( R

Consider the previous assembly program.

LD FR

LD FR

ADD.D F F F

MUL.D F F F

BEQZ R TARGET

SUB.D F F F

DIV.D F F F

ADD.D F F F

TARGET: SUB.D F F F

SD FR

ADD.D F F F

Consider a processor performing dynamic scheduling with Tomasulos algorithm and Reorder Buffer.

The processor has the following unpipelined execution units: Integer Unit latency: clock cycle FP

Adders latency: clock cycles FP Divider latency: clock cycles FP Multiplier latency: clock

cycles and Memory Unit latency: clock cycle including address computation and memory access

The processor has three sets of reservation stations: one shared by the adders and the integer unit Addx

one for the memory Loadx and one shared by multiplier and divider Multx

The ROB has entries.

Assume that branch target and condition are computed by the Integer Unit. In the presence of a branch, the processor

will by default take the fallthrough path.

Assume R R Mem Mem

Use the tables provided in the next pages to walk through the execution of the code in the following four situations:

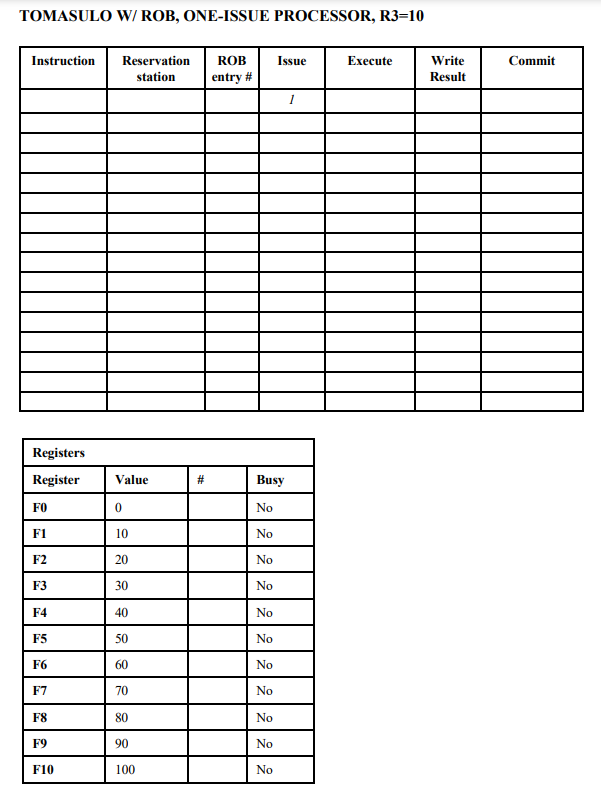

a Oneissue processor, Tomasulo ROB, R

b Oneissue processor, Tomasulo ROB, R

c Fourissue processor, Tomasulo ROB, R

In all cases, the reservation stations and reorder buffer tables are provided at the end for your convenience. You do

not need to fill these tables however you need to know what they are for You are required only to fill:

The table indicating the progress of the instruction, cycle by cycle. In this table you should also indicate the

tag of the reservation station and the ROB entry used by the instruction.

The final value of the registers.

When flushing the ROB, please strike out the instructions and do not delete them from the table

In filling the tables, please assume that:

If an instruction I is using a ROB entry, such ROB entry becomes available and can be used in the clock

cycle after I commits.

If an instruction I uses a reservation station or an execution unit, such reservation stationexecution unit is

freed when I writes the result, and is available to a different instruction starting from the next clock cycle.

Question : Why dont we need to wait until I is completely done?

If an instruction J depends on instruction I, the data written by instruction I will be available to J in the clock

cycle when I writes the result say t and in the absence of data hazard instruction J will be able to execute

in the following clock cycle say t

Question : In the presence of a ROB, why dont we need to wait

until I commits?

If the branch is mispredicted, the target instruction of the branch is fetched in the clock cycle after the branch

instruction commits.

Question : The presence of the ROB and of the commit stage allows handling exceptions in a dynamically scheduled

processor. Why?

Provide a clear but concise answer to the questions and fill in the table for cases:

TOMASULO W ROB, ONEISSUE PROCESSOR, R

TOMASULO W ROB, ONEISSUE PROCESSOR, R

TOMASULO W ROB, FOURISSUE PROCESSOR, R

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock