Question: Consider the processor (on right) with two-level cache hierarchy. Suppose that 65% of benchmark A's instructions are accessed from the L1 cache, whereas the

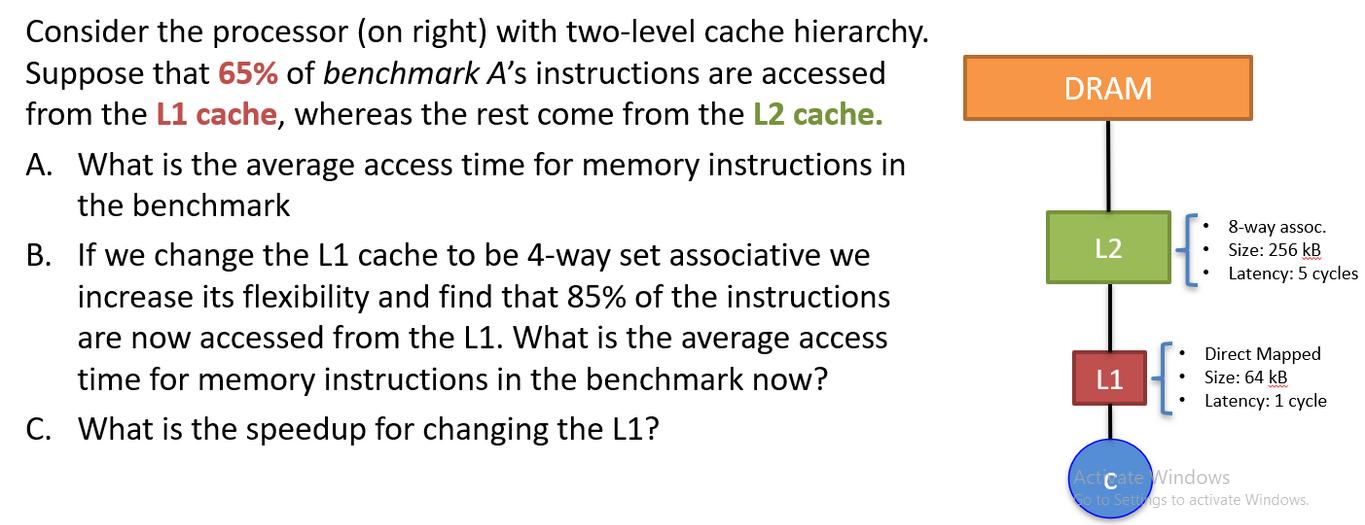

Consider the processor (on right) with two-level cache hierarchy. Suppose that 65% of benchmark A's instructions are accessed from the L1 cache, whereas the rest come from the L2 cache. A. What is the average access time for memory instructions in the benchmark B. If we change the L1 cache to be 4-way set associative we increase its flexibility and find that 85% of the instructions are now accessed from the L1. What is the average access time for memory instructions in the benchmark now? C. What is the speedup for changing the L1? DRAM L2 8-way assoc. Size: 256 kB Latency: 5 cycles Direct Mapped Size: 64 kB Latency: 1 cycle Acticate Windows Go to Settings to activate Windows.

Step by Step Solution

There are 3 Steps involved in it

Heres how to solve it Part A Calculate the miss rate for the L1 cache1 65 35 Calculate the average access time for the L1 cache1 cycle 65 5 cycles 35 ... View full answer

Get step-by-step solutions from verified subject matter experts