Question: Could someone please show me what the sequential network looks like for this question? Along with the symbol? Thank you in advance! Sequential Networlk You

Could someone please show me what the sequential network looks like for this question? Along with the symbol? Thank you in advance!

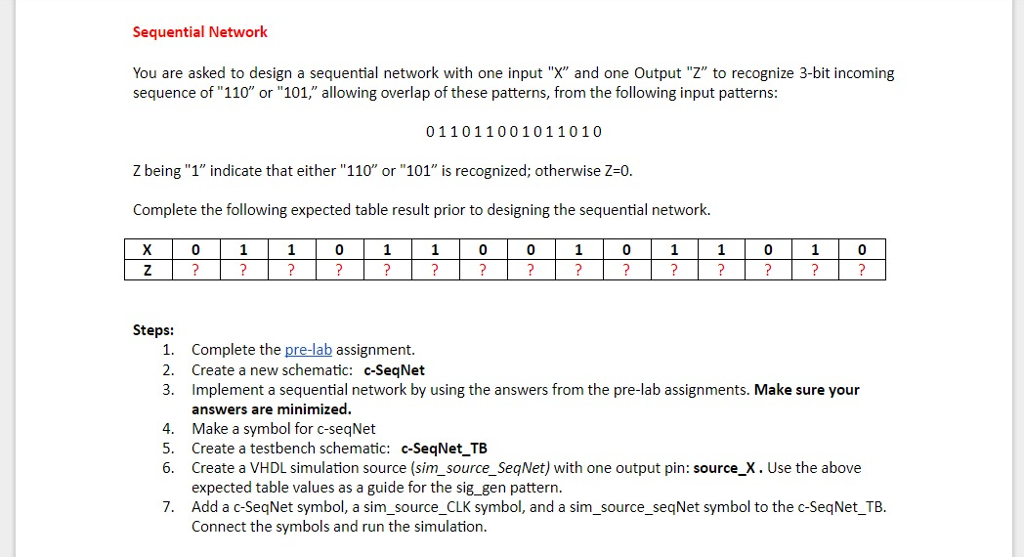

Sequential Networlk You are asked to design a sequential network with one input "X" and one Output "Z" to recognize 3-bit incoming sequence of "110" or "101," allowing overlap of these patterns, from the following input patterns 011011001011010 Z being "1" indicate that either "110" or "101" is recognized; otherwise Z-0. Complete the following expected table result prior to designing the sequential network. 0 1 0 0 0 0 0 Steps: 1. Complete the pre-lab assignment. 2. Create a new schematic: c-SeqNet 3. Implement a sequential network by using the answers from the pre-lab assignments. Make sure your answers are minimized. 4. Make a symbol for c-seqNet 5. Create a testbench schematic: c-SeqNet TB 6. Create a VHDL simulation source (sim_source_SeqNet) with one output pin: source_X. Use the above expected table values as a guide for the sig_gen pattern Add a c-SegNet symbol, a sim source CLK symbol, and a sim source segNet symbol to the c-SegNet TB. Connect the symbols and run the simulation 7. Sequential Networlk You are asked to design a sequential network with one input "X" and one Output "Z" to recognize 3-bit incoming sequence of "110" or "101," allowing overlap of these patterns, from the following input patterns 011011001011010 Z being "1" indicate that either "110" or "101" is recognized; otherwise Z-0. Complete the following expected table result prior to designing the sequential network. 0 1 0 0 0 0 0 Steps: 1. Complete the pre-lab assignment. 2. Create a new schematic: c-SeqNet 3. Implement a sequential network by using the answers from the pre-lab assignments. Make sure your answers are minimized. 4. Make a symbol for c-seqNet 5. Create a testbench schematic: c-SeqNet TB 6. Create a VHDL simulation source (sim_source_SeqNet) with one output pin: source_X. Use the above expected table values as a guide for the sig_gen pattern Add a c-SegNet symbol, a sim source CLK symbol, and a sim source segNet symbol to the c-SegNet TB. Connect the symbols and run the simulation 7

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts