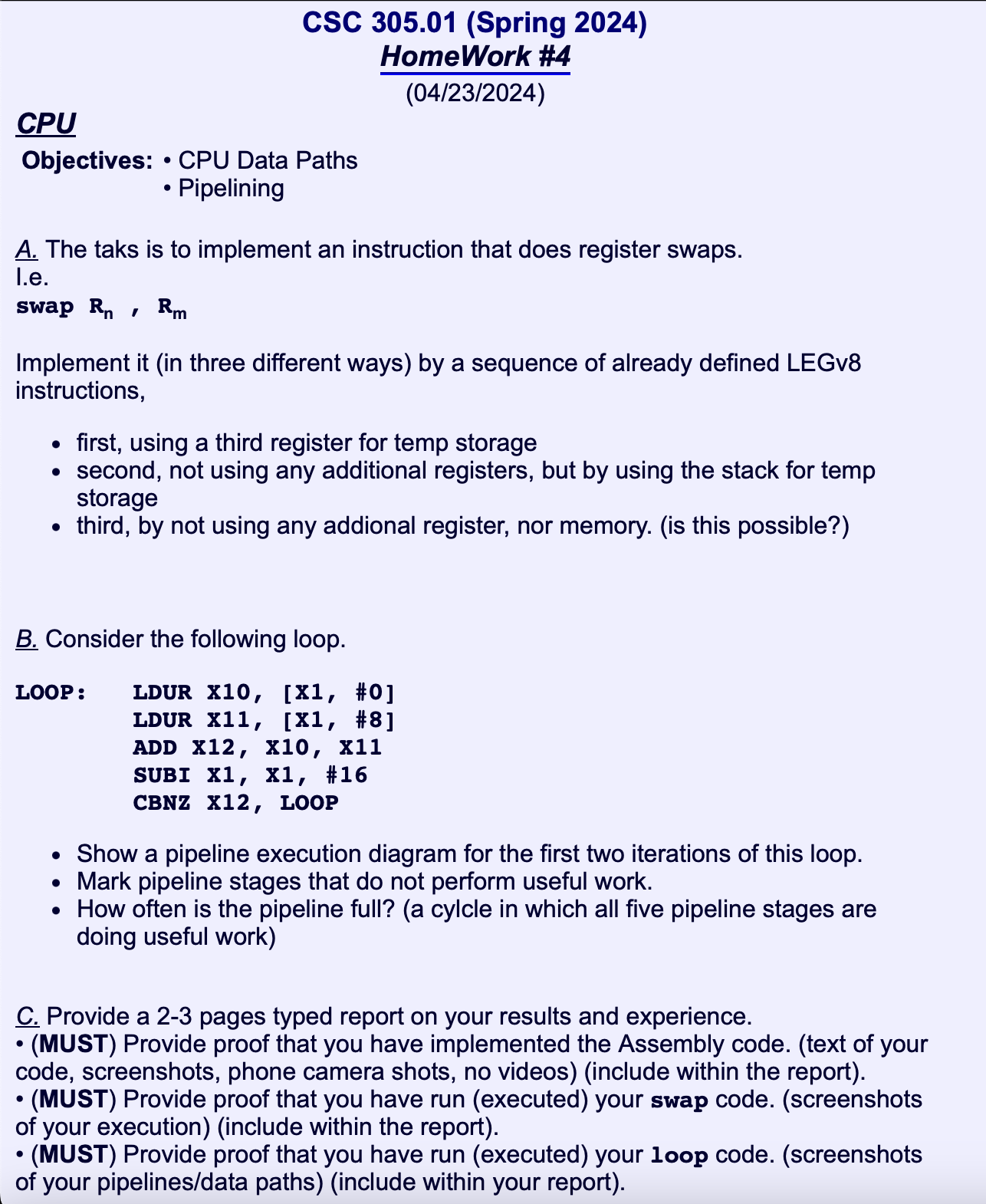

Question: CSC 3 0 5 . 0 1 ( Spring 2 0 2 4 ) HomeWork # 4 ( 0 4 2 3 ? 2 0

CSC Spring

HomeWork #

CPU

Objectives: CPU Data Paths

Pipelining

A The taks is to implement an instruction that does register swaps.

I.e

swap

Implement it in three different ways by a sequence of already defined LEGv

instructions,

first, using a third register for temp storage

second, not using any additional registers, but by using the stack for temp

storage

third, by not using any addional register, nor memory. is this possible?

B Consider the following loop.

LOOP: LDUR XX #

LDUR #

ADD

SUBI #

CBNZ X LOOP

Show a pipeline execution diagram for the first two iterations of this loop.

Mark pipeline stages that do not perform useful work.

How often is the pipeline full? a cylcle in which all five pipeline stages are

doing useful work

C Provide a pages typed report on your results and experience.

MUST Provide proof that you have implemented the Assembly code. text of your

code, screenshots, phone camera shots, no videosinclude within the report

MUST Provide proof that you have run executed your swap code. screenshots

of your executioninclude within the report

MUST Provide proof that you have run executed your loop code. screenshots

of your pipelinesdata pathsinclude within your report

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock