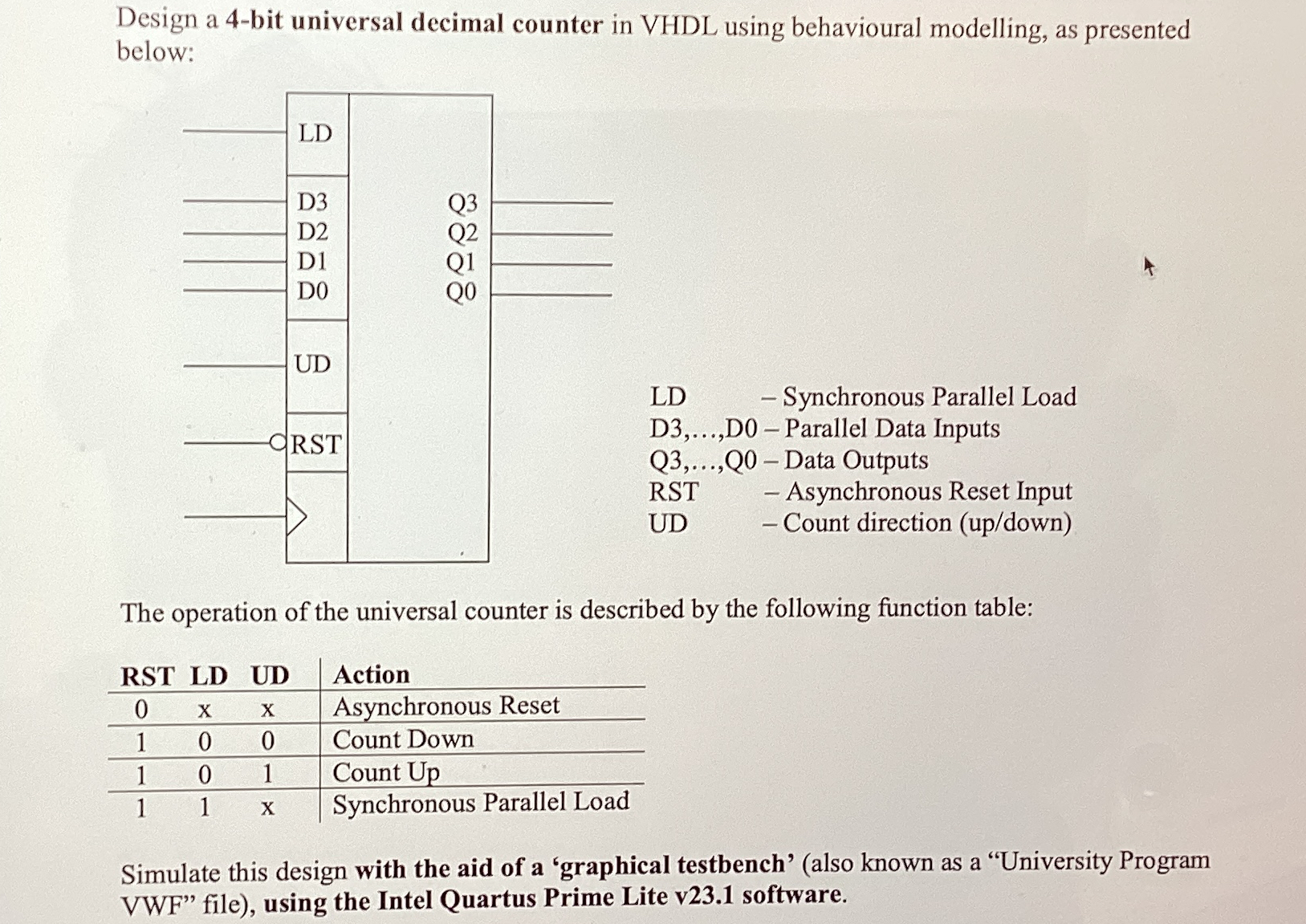

Question: Design a 4 - bit universal decimal counter in VHDL using behavioural modelling, as presented below: LD - Synchronous Parallel Load D 3 , .

Design a bit universal decimal counter in VHDL using behavioural modelling, as presented below:

LD Synchronous Parallel Load

DD Parallel Data Inputs

QQQ Data Outputs

RST Asynchronous Reset Input

UD Count direction updown

The operation of the universal counter is described by the following function table:

tableRSTLDUDActionxxAsynchronous ResetCount DownCount UpxSynchronous Parallel Load

Simulate this design with the aid of a 'graphical testbench' also known as a "University Program VWF file using the Intel Quartus Prime Lite v software.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock