Question: Design a 6 - bit, shift - right register with D flip flops, and use it to implement a circuit that detects the sequence

Design a bit, shiftright register with D flip flops, and use it to implement a circuit that detects the sequence the rightmost bit is the first arriving

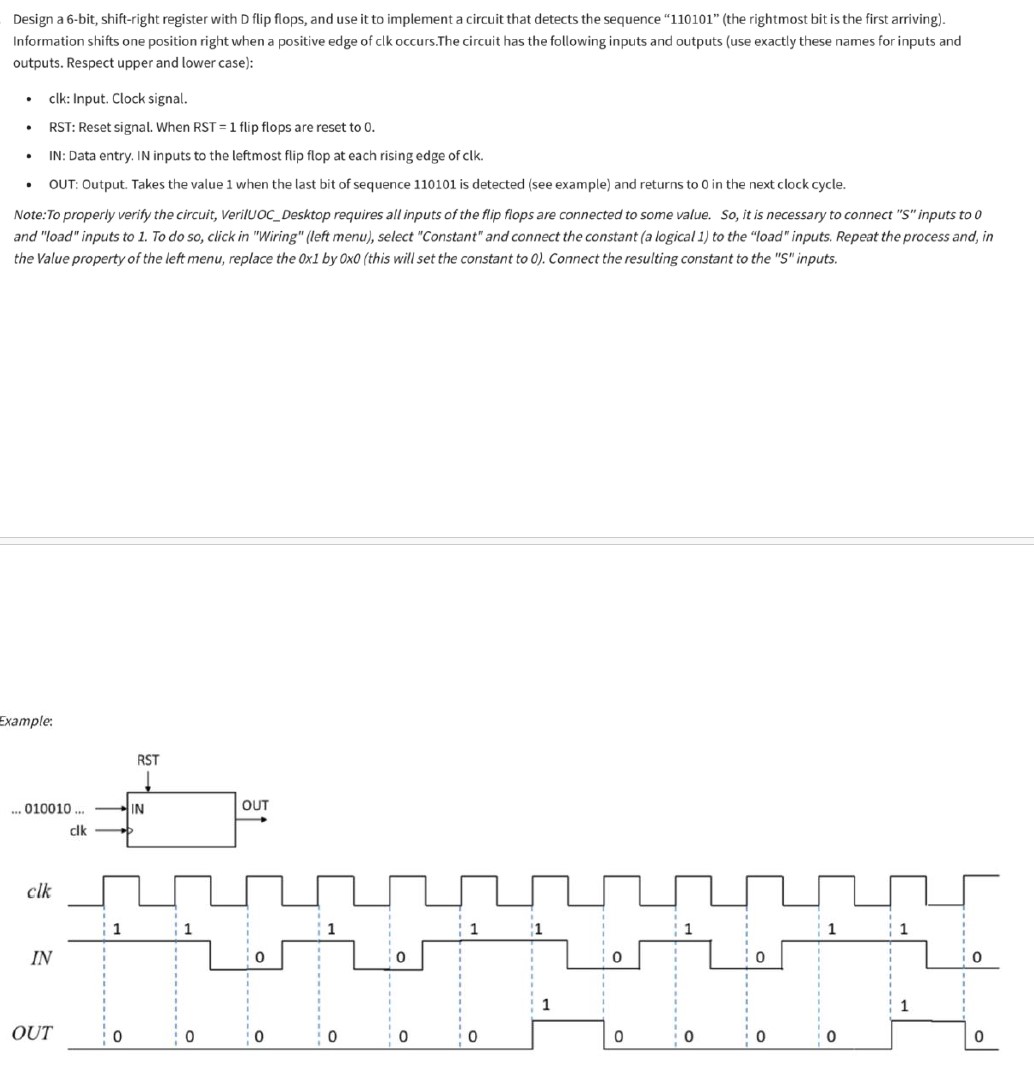

Information shifts one position right when a positive edge of clk occurs. The circuit has the following inputs and outputs use exactly these names for inputs and

outputs. Respect upper and lower case:

clk: Input. Clock signal.

RST: Reset signal. When RST flip flops are reset to

IN: Data entry. IN inputs to the leftmost flip flop at each rising edge of clk

OUT: Output. Takes the value when the last bit of sequence is detected see example and returns to in the next clock cycle.

Note:To properly verify the circuit, VerilUOCDesktop requires all inputs of the flip flops are connected to some value. So it is necessary to connect S inputs to

and "load" inputs to To do so click in "Wiring" left menu select "Constant" and connect the constant a logical to the "load" inputs. Repeat the process and, in

the Value property of the left menu, replace the by this will set the constant to Connect the resulting constant to the inputs.

Example:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock