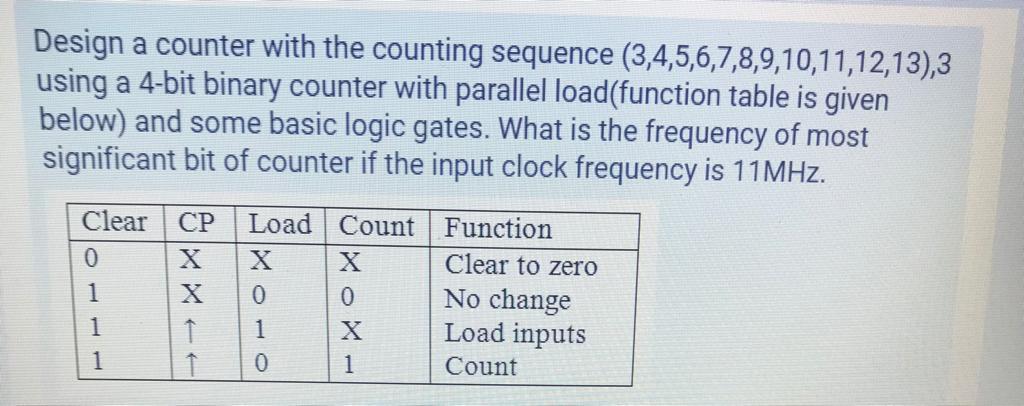

Question: Design a counter with the counting sequence (3,4,5,6,7,8,9,10,11,12,13),3 using a 4-bit binary counter with parallel load(function table is given below) and some basic logic gates.

Design a counter with the counting sequence (3,4,5,6,7,8,9,10,11,12,13),3 using a 4-bit binary counter with parallel load(function table is given below) and some basic logic gates. What is the frequency of most significant bit of counter if the input clock frequency is 11 MHz. Clear Load 0 1 X 0 1 0 X 1 Count Function X Clear to zero No change X Load inputs 1 Count 1 1 Design a counter with the counting sequence (3,4,5,6,7,8,9,10,11,12,13),3 using a 4-bit binary counter with parallel load(function table is given below) and some basic logic gates. What is the frequency of most significant bit of counter if the input clock frequency is 11 MHz. Clear Load 0 1 X 0 1 0 X 1 Count Function X Clear to zero No change X Load inputs 1 Count 1 1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts