Question: Design a high - level state machine that implements a 3 2 - bit binary multiplier. The system's word size should be 3 2 bits.

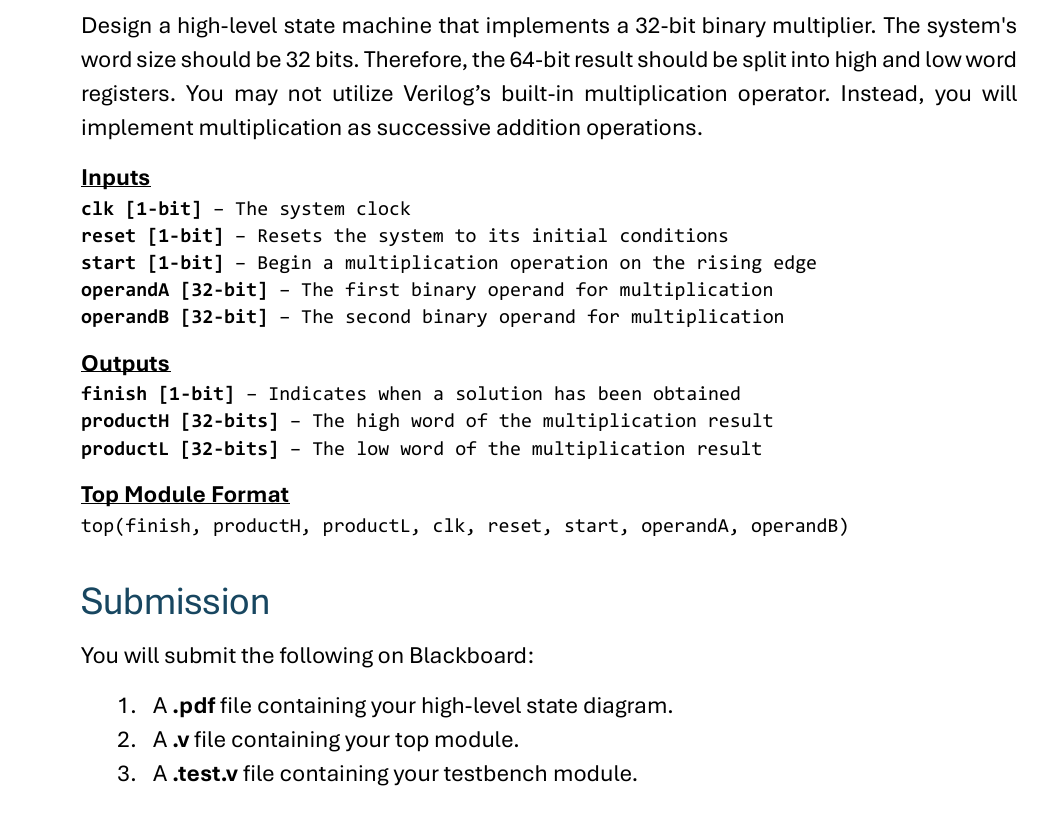

Design a highlevel state machine that implements a bit binary multiplier. The system's word size should be bits. Therefore, the bit result should be split into high and low word registers. You may not utilize Verilog's builtin multiplication operator. Instead, you will implement multiplication as successive addition operations.

Inputs

clk bit The system clock

reset bit Resets the system to its initial conditions

start bit Begin a multiplication operation on the rising edge

operandA bit The first binary operand for multiplication

operandB bit The second binary operand for multiplication

Outputs

finish bit Indicates when a solution has been obtained

productH bits The high word of the multiplication result

productL bits The low word of the multiplication result

Top Module Format

Submission

You will submit the following on Blackboard:

A pdf file containing your highlevel state diagram.

A v file containing your top module.

A test.v file containing your testbench module.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock