Question: Design a static CMOS circuit to compute F = AB + DE. Sketch an implementation using AOI, NAND +INV. Label each gate with the width

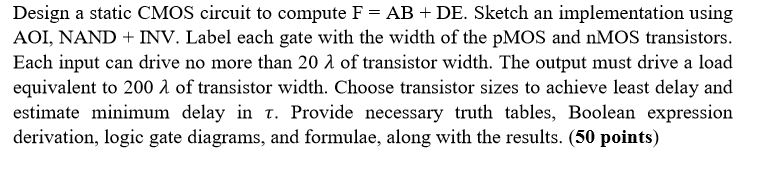

Design a static CMOS circuit to compute F = AB + DE. Sketch an implementation using AOI, NAND +INV. Label each gate with the width of the pMOS and nMOS transistors. Each input can drive no more than 20 of transistor width. The output must drive a load equivalent to 200 of transistor width. Choose transistor sizes to achieve least delay and estimate minimum delay in t. Provide necessary truth tables, Boolean expression derivation, logic gate diagrams, and formulae, along with the results. (50 points) Design a static CMOS circuit to compute F = AB + DE. Sketch an implementation using AOI, NAND +INV. Label each gate with the width of the pMOS and nMOS transistors. Each input can drive no more than 20 of transistor width. The output must drive a load equivalent to 200 of transistor width. Choose transistor sizes to achieve least delay and estimate minimum delay in t. Provide necessary truth tables, Boolean expression derivation, logic gate diagrams, and formulae, along with the results. (50 points)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts