Question: Design a Verilog module that will implement the Shift - and - Subtract division algorithm for unsigned integers. The algorithm will perform the following function

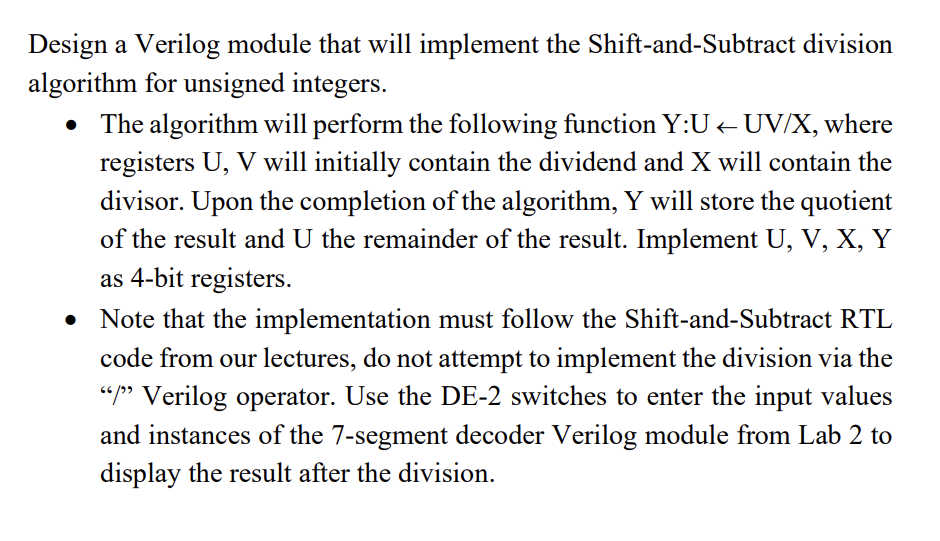

Design a Verilog module that will implement the ShiftandSubtract division

algorithm for unsigned integers.

The algorithm will perform the following function :UlarrU where

registers will initially contain the dividend and will contain the

divisor. Upon the completion of the algorithm, will store the quotient

of the result and U the remainder of the result. Implement U V X Y

as bit registers.

Note that the implementation must follow the ShiftandSubtract RTL

code from our lectures, do not attempt to implement the division via the

Verilog operator. Use the DE switches to enter the input values

and instances of the segment decoder Verilog module from Lab to

display the result after the division.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock