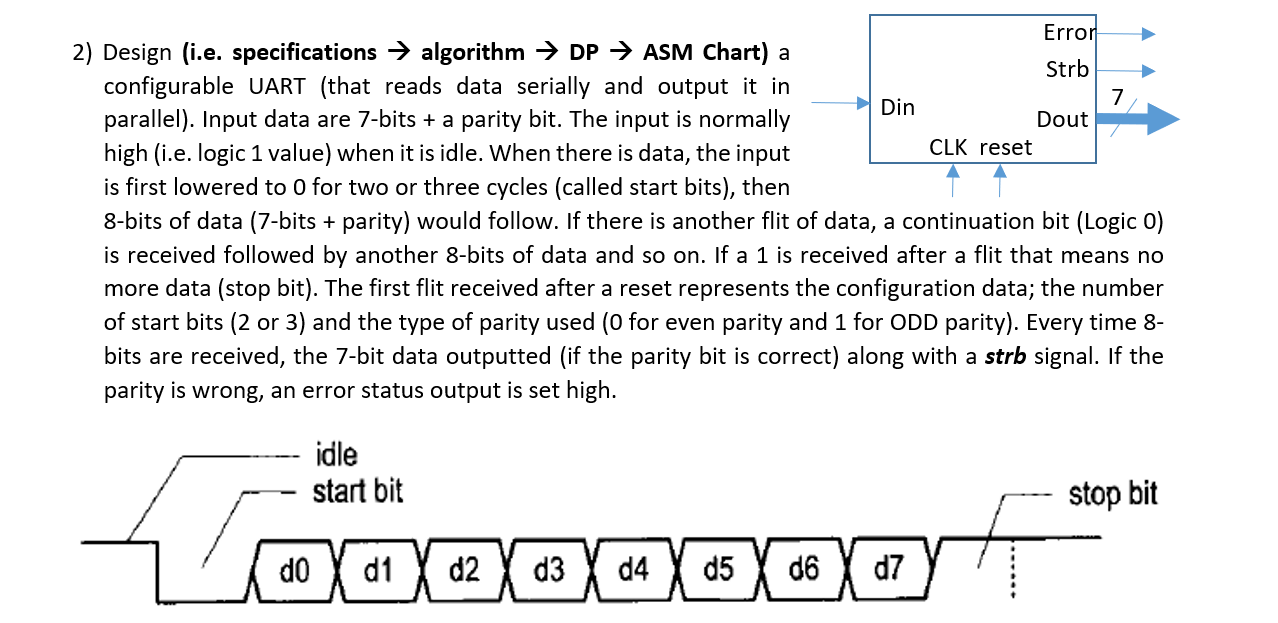

Question: Design ( i . e . specifications algorithm DP ASM Chart ) a configurable UART ( that reads data serially and output it in parallel

Design ie specifications algorithm DP ASM Chart a

configurable UART that reads data serially and output it in

parallel Input data are bits a parity bit. The input is normally

high ie logic value when it is idle. When there is data, the input

is first lowered to for two or three cycles called start bits then

bits of data bits parity would follow. If there is another flit of data, a continuation bit Logic

is received followed by another bits of data and so on If a is received after a flit that means no

more data stop bit The first flit received after a reset represents the configuration data; the number

of start bits or and the type of parity used for even parity and for ODD parity Every time

bits are received, the bit data outputted if the parity bit is correct along with a strb signal. If the

parity is wrong, an error status output is set high.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock