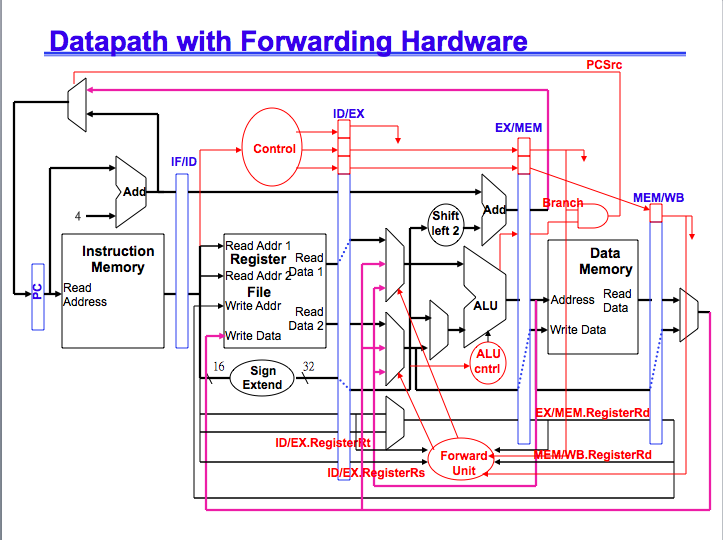

Question: Design the above forward unit that can resolve the data hazard for the MIPS pipelined processor: ->The available components you can use include the basic

Design the above forward unit that can resolve the data hazard for the MIPS pipelined processor:

->The available components you can use include the basic logic gates (inverter, and, or, nand, nor) and comparators.

->The input will be 20 bits, and output 4 bits

->First of all, use the comparators to generate the required signals from cross-checking the 4 inputs with each 5 bits.

->Then write down the boolean functions for the 2 outputs with each 2 bits for controlling the two multiplexors before the ALU.

->Draw your circuit diagram with the comparators and logic gates.

Datapath with Forwarding Hardware PCSrc IDIEX EXIMEM Control IF/ID Ad MEM/WB hi left 2 Read Addr 1 Data Instruction Memory Register Read Read Addr Data 1 Memory File rite Addr Read Data Read ddress ALU Read Data 2 Write Data Data AL cntrl 16Sigrn 32 Extend XIMEM.RegisterRd IDIEX.RegisterRt RegisterRd Forward- gisterRs Unit Datapath with Forwarding Hardware PCSrc IDIEX EXIMEM Control IF/ID Ad MEM/WB hi left 2 Read Addr 1 Data Instruction Memory Register Read Read Addr Data 1 Memory File rite Addr Read Data Read ddress ALU Read Data 2 Write Data Data AL cntrl 16Sigrn 32 Extend XIMEM.RegisterRd IDIEX.RegisterRt RegisterRd Forward- gisterRs Unit

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts