Question: Detail please! Type and attach a Verilog^1 module to do the following: Input a 4-bit data word, Generate an 8-bit Hamming Code codeword by adding

Detail please!

Detail please!

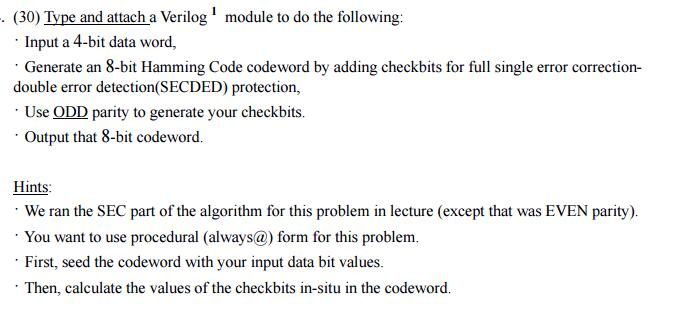

Type and attach a Verilog^1 module to do the following: Input a 4-bit data word, Generate an 8-bit Hamming Code codeword by adding check bits for full single error correction-double error detection(SECDED) protection, Use ODD parity to generate your check bits. Output that 8-bit codeword. We ran the SEC part of the algorithm for this problem in lecture (except that was EVEN parity). You want to use procedural (always@) form for this problem. First, seed the codeword with your input data bit values. Then, calculate the values of the check bits in-situ in the codeword

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts