Question: Digital Logic Design Fall20 Question 1 Not yet answered A 22-MHz clock signal is used into a 4-bit Ripple counter (Frequency division) circuit. What will

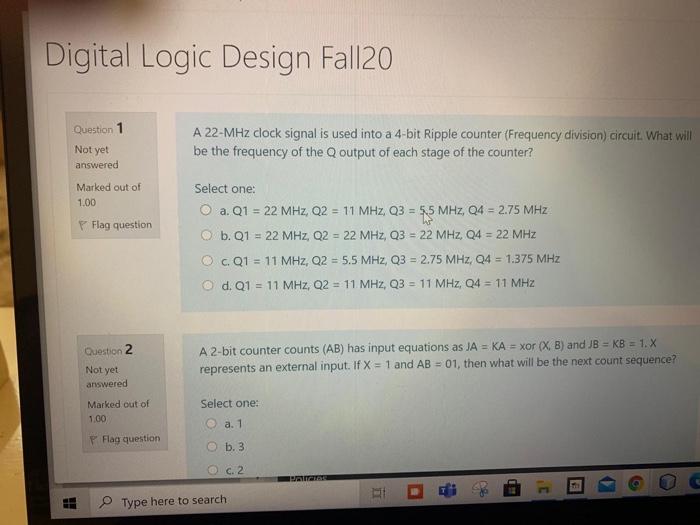

Digital Logic Design Fall20 Question 1 Not yet answered A 22-MHz clock signal is used into a 4-bit Ripple counter (Frequency division) circuit. What will be the frequency of the Qoutput of each stage of the counter? Marked out of 1.00 Flag question Select one: a. Q1 = 22 MHz, Q2 = 11 MHz, Q3 = 5,5 MHz, 04 = 2.75 MHz w b. Q1 = 22 MHz, Q2 = 22 MHz, Q3 = 22 MHz, Q4 = 22 MHz O c. Q1 = 11 MHz, Q2 = 5.5 MHz, Q3 = 2.75 MHz, Q4 = 1.375 MHz d. Q1 = 11 MHz, Q2 = 11 MHz, Q3 = 11 MHz, 24 = 11 MHz Question 2 A 2-bit counter counts (AB) has input equations as JA = KA = xor (XB) and JB = KB = 1. X represents an external input. If X = 1 and AB = 01, then what will be the next count sequence? Not yet answered Marked out of 1.00 Select one: a. 1 P Flag question 6.3 c. 2 TAT - Type here to search

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts