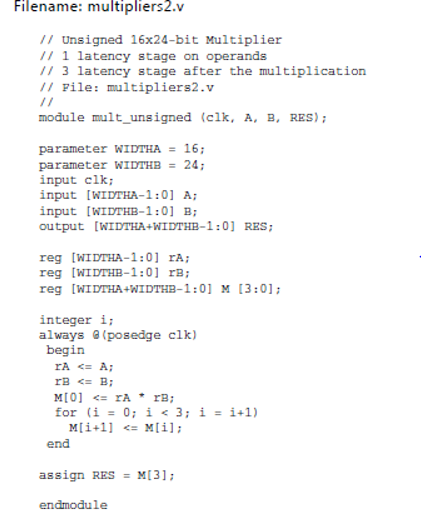

Question: Draw the functionality implemented by Verilog code below including the pipeline registers. Note comments will be masked in non-sample exam Filename: multipliers2.v//Unsigned 16 times 24-bit

Draw the functionality implemented by Verilog code below including the pipeline registers. Note comments will be

masked in non-sample exam

Filename: multipliers2.v//Unsigned 16 times 24-bit Multiplier//1 latency stage on operands//3 latency stage after the multiplication//File: multipliers2.v//module mult_unsigned (clk, A, B, RES); parameter WIDTHA = 16; parameter WIDTHS = 24; input clk; input [WIDTHA-1:0] A; input [WIDTHB-1:0] B; output [WIDTHA+WTDTHB-1:0] RES; reg [WIETHA-1:0] rA; reg [WIDTHB-1:0] rB; reg [WIETHA+WIDTHB-1:01 M [3:0]; integer i; always @ (posedge clk) begin rA

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts