Question: Equations included According to data collected with your application using the original ISA, 10% of loads have a load-to-ALU data hazard that the compiler does

Equations included

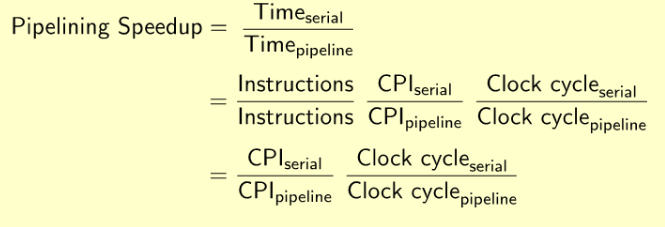

According to data collected with your application using the original ISA, 10% of loads have a load-to-ALU data hazard that the compiler does not remove. Assuming no change in clock speed, use this data, together with the other data given above, to find the overall expected speedup of the 4-stage design over the original 5-stage MIPS architecture.

Here are the equations involved:

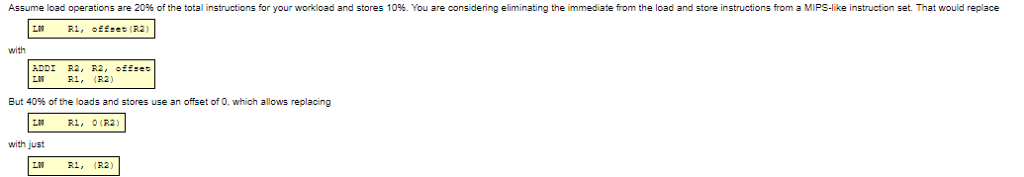

Assume load operations are 20% o the total instructions for your workload and stores 1 0%. You are considering eliminating the immediate om the load and store instructions o a MIPS ke instruction set. That would replace with R1, R2) But 40% of the loads and stores use an offset of 0, which allows replacing with just R1, R2) Assume load operations are 20% o the total instructions for your workload and stores 1 0%. You are considering eliminating the immediate om the load and store instructions o a MIPS ke instruction set. That would replace with R1, R2) But 40% of the loads and stores use an offset of 0, which allows replacing with just R1, R2)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts