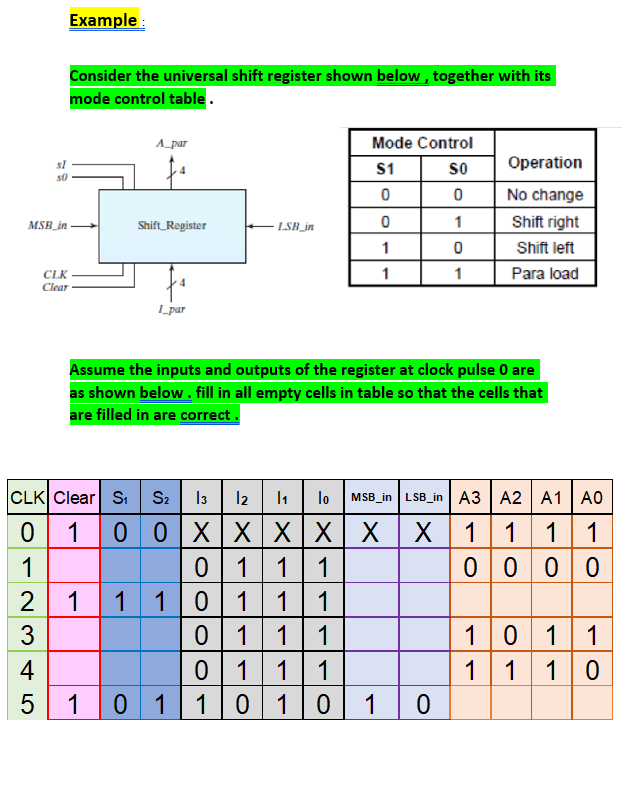

Question: Example Consider the universal shift register shown below, together with its mode control table A_par Mode Control S1 SO 0 0 14 50 Operation MSB_in

Example Consider the universal shift register shown below, together with its mode control table A_par Mode Control S1 SO 0 0 14 50 Operation MSB_in Shift_Register ISB_jr 1 0 1 1 No change Shift right Shift left Para load 0 1 CLK Clear Lpar Assume the inputs and outputs of the register at clock pulse 0 are as shown below. fill in all empty cells in table so that the cells that are filled in are correct. CLK Clear S1 S2 13 12 11 lo MSB_in LSB_in A3 A2A1AO 0 1 0 0 X X X X X X XX 11 1 1 1 0111 0 0 0 0 2 1 1 10 111 3 0 1 11 1 0 1 1 4 0 111 1 1 1 0 5 1 0 1 10 10 11 1 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts