Question: Exercise 1 (9 pts) We have seen that ARM has 16*32 bits registers (plus floating point registers) There is also a status register: CPSR. It

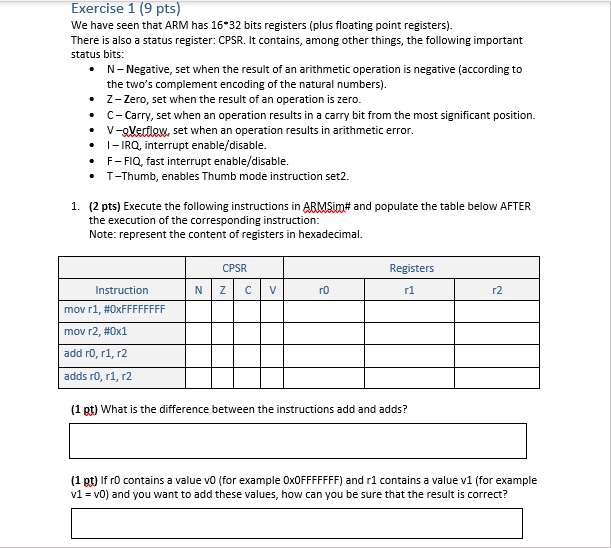

Exercise 1 (9 pts) We have seen that ARM has 16*32 bits registers (plus floating point registers) There is also a status register: CPSR. It contains, among other things, the following important status bits N Negative, set when the result of an arithmetic operation is negative (according to the two's complement encoding of the natural numbers . Z- Zero, set when the result of an operation is zero . C Carry, set when an operation results in a carry bit from the most significant position. V-9Verflow, set when an operation results in arithmetic error I-IRQ, interrupt enable/disable . F FIQ, fast interrupt enable/disable. T-Thumb, enables Thumb mode instruction set2. * . . I. (2 pts) Execute the following instructions in ARMSim# and populate the table below AFTER the execution of the corresponding instruction Note: represent the content of registers in hexadecimal CPSR Registers Instruction ro r1 r2 mov r1#0xFFFFFFFF mov r2#0x1 add rO, r1, r2 adds rO, r1, r2 , , (1 pt) What is the difference between the instructions add and adds? (1 pt) If r0 contains a value vO (for example 0xOFFFFFFF) and r1 contains a value v1 (for example v1v) and you want to add these values, how can you be sure that the result is correct

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts