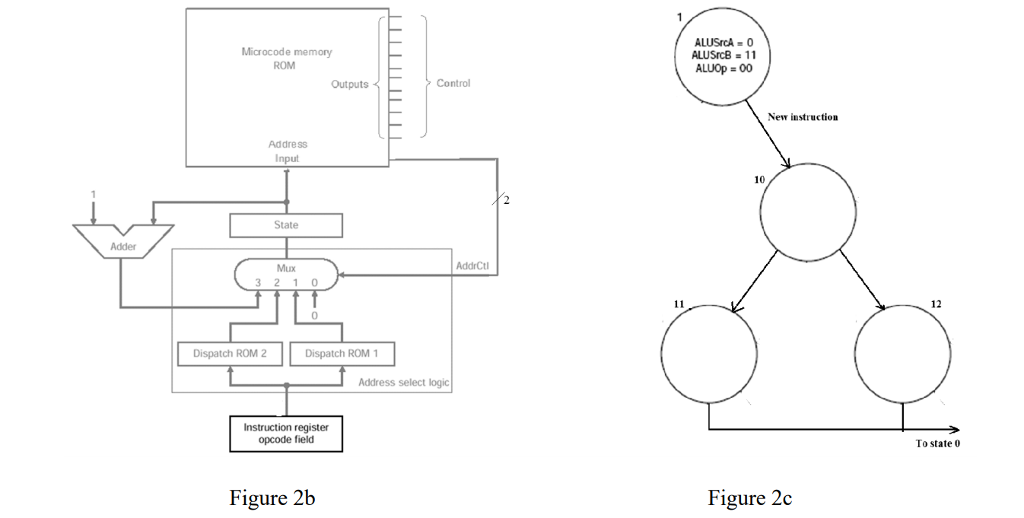

Question: Figure 2b shows a microcode circuit to control a multicycle data path microprocessor. The controller synchronous sequential state machine diagram is shown in figure 4b.

Figure 2b shows a microcode circuit to control a multicycle data path microprocessor. The controller synchronous sequential state machine diagram is shown in figure 4b.

i. With reference to figure 4b, describe the operation of the circuit noting how the ROMs in figure 2b are used.

ii. If a new instruction is to be added that requires additional states as shown in figure 2c, describe how the circuit in figure 2b is modified and used.

Microcode memory ROM ALUSrcA 0 ALUSrcB = 11 ALUOp 00 Control Outputs New instruction Address Input State Adder Mux 12 0 Dispatch ROM 2 Dispatch ROM Address select logic Instruction register opcode field To state 0 Figure 2b Figure 2c Microcode memory ROM ALUSrcA 0 ALUSrcB = 11 ALUOp 00 Control Outputs New instruction Address Input State Adder Mux 12 0 Dispatch ROM 2 Dispatch ROM Address select logic Instruction register opcode field To state 0 Figure 2b Figure 2c

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts