Question: For each entry in the F1 table (Table 7-2), translate it into the actual needed signals by name. Include the two multiplexorb(call it muxA, the

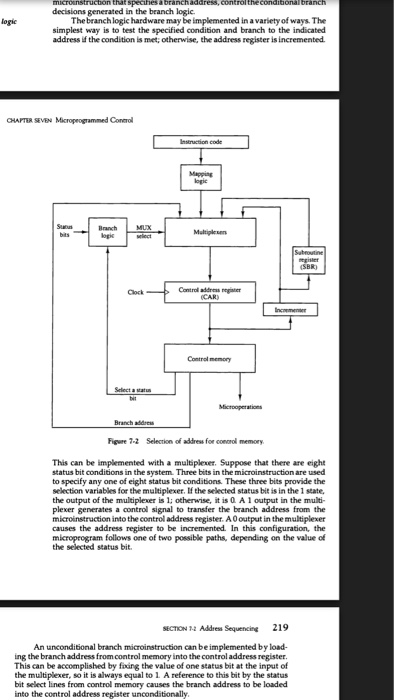

decisions generated in the branch logic. logic Thebranch logic hardware may be implemented in a variety of ways. The simplest way is to test the specified condition and branch to the indicated address if the condition is met, otherwise, the address r register is incremented CHAPTER SEVEN Micropeogrammed Conrol ogic BranchMUX bts ogik (SBR) Clock Controi addrs rogner Branch aodres Figure 7-2 Selection of address for conarol memory This can be implemented with a multiplexer. Suppose that there are eight status bit conditions in the system. Three bits in the microinstruction are used to specify any one of eight status bit conditions These three bits provide the selection variables for the multiplexer. If the selected status bit is in the 1 state, the output of the multiplexer is 1: otherwise, it is Q A 1 output in the multi- plexer generates a control signal to transfer the branch address from the microinstruction into the control address register. A0output in the multiplexer causes the address register to be incremented. In this configuration, the microprogram follows one of two possible paths, depending on the value of the selected status bit. SECTION 14 Address Sequencig 219 An unconditional branch microinstruction can be implemented by load- ng the branch address from control memory into the control address register This can be accomplished by faing the value of one status bit at the input of the multiplexer, so it is always equal to 1 A reference to this bit by the status bit select lines from control memory causes the branch address to be loaded into the control address register unconditionally decisions generated in the branch logic. logic Thebranch logic hardware may be implemented in a variety of ways. The simplest way is to test the specified condition and branch to the indicated address if the condition is met, otherwise, the address r register is incremented CHAPTER SEVEN Micropeogrammed Conrol ogic BranchMUX bts ogik (SBR) Clock Controi addrs rogner Branch aodres Figure 7-2 Selection of address for conarol memory This can be implemented with a multiplexer. Suppose that there are eight status bit conditions in the system. Three bits in the microinstruction are used to specify any one of eight status bit conditions These three bits provide the selection variables for the multiplexer. If the selected status bit is in the 1 state, the output of the multiplexer is 1: otherwise, it is Q A 1 output in the multi- plexer generates a control signal to transfer the branch address from the microinstruction into the control address register. A0output in the multiplexer causes the address register to be incremented. In this configuration, the microprogram follows one of two possible paths, depending on the value of the selected status bit. SECTION 14 Address Sequencig 219 An unconditional branch microinstruction can be implemented by load- ng the branch address from control memory into the control address register This can be accomplished by faing the value of one status bit at the input of the multiplexer, so it is always equal to 1 A reference to this bit by the status bit select lines from control memory causes the branch address to be loaded into the control address register unconditionally

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts