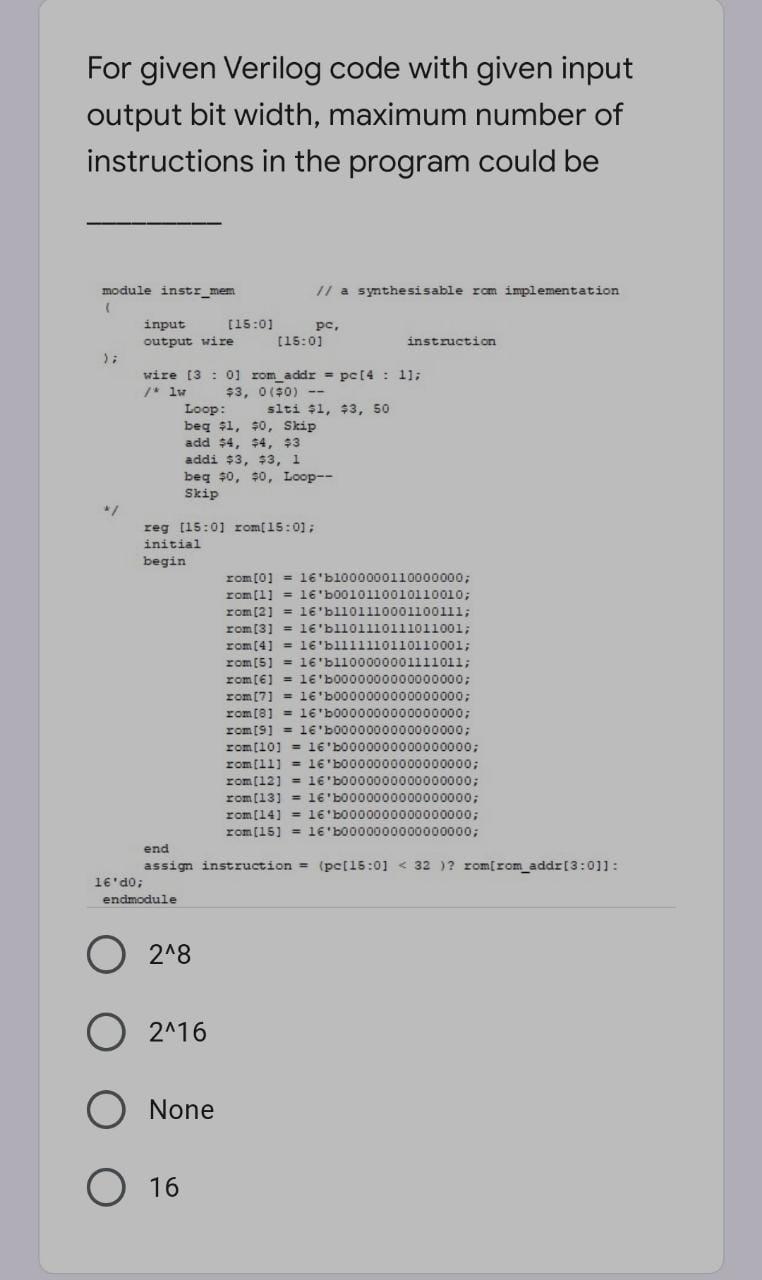

Question: For given Verilog code with given input output bit width, maximum number of instructions in the program could be module instr_mem // a synthesisable

For given Verilog code with given input output bit width, maximum number of instructions in the program could be module instr_mem // a synthesisable ram implementation input [15:0] pc, output wire (15:0] instruction wire (3 : 01 rom addr = pc[4 : 11; /* lw $3, 0($0) -- Loop: beq $1, $0, Skip add $4, $4, $3 addi $3, $3, 1 slti $1, $3, 50 beg $0, 40, Loop-- Skip */ reg [15:01 rom[15:01; initial begin rom[0] = 1E'bl000000110000000; rom(1] = 1E'b0010110010110010; rom [2] = 1E'bl101110001100111; rom[3] = 1E'bll01110111011001; rom[4] = 16'bll11110110110001; rom[5] = 16'bl100000001111011; rom[6] = 1'b0000000000000000; rom[7] = 1'b0000000000000000; rom[8] = 16'b0000000000000000; rom[9] = 16'b0000000000000000; rom(10] = 1'b0000000000000000; rom[l1] = 1'b0000000000000000; rom(12] = 16'b0000000000000000; rom(13] = 1'b0000000000000000; rom[14] = 16'b0000000000000000; rom(15) = 16'b00000000000000003B end assign instruction = (pc[15:01 < 32 )? rom[rom_addr[3:011: 16'do; endmodule O 2^8 2^16 O None 16

Step by Step Solution

3.35 Rating (164 Votes )

There are 3 Steps involved in it

option d will be correct The instr... View full answer

Get step-by-step solutions from verified subject matter experts