Question: FOR OPERATING SYSTEMS: Q5. Suppose, on a machine with 16-bit virtual and physical addresses and a page size of 256 bytes, a process is running

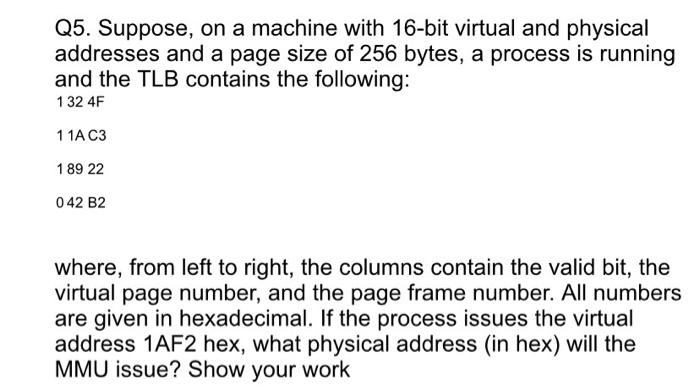

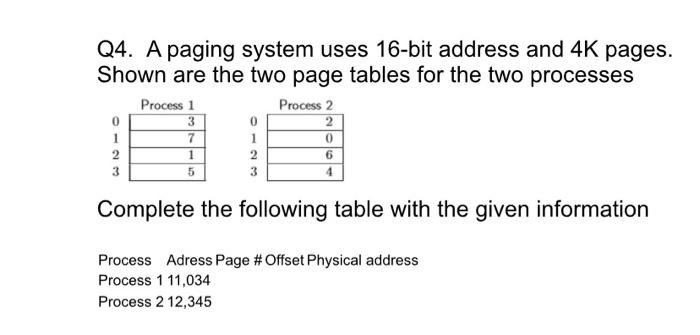

Q5. Suppose, on a machine with 16-bit virtual and physical addresses and a page size of 256 bytes, a process is running and the TLB contains the following: 132 4F 1 1A C3 1 89 22 042 B2 where, from left to right, the columns contain the valid bit, the virtual page number, and the page frame number. All numbers are given in hexadecimal. If the process issues the virtual address 1AF2 hex, what physical address (in hex) will the MMU issue? Show your work Q4. A paging system uses 16-bit address and 4K pages. Shown are the two page tables for the two processes Process 2 0 7 Process 1 3 0 1 2 3 1 2 1 5 2 0 6 4 Complete the following table with the given information Process Adress Page #Offset Physical address Process 1 11,034 Process 2 12,345

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts