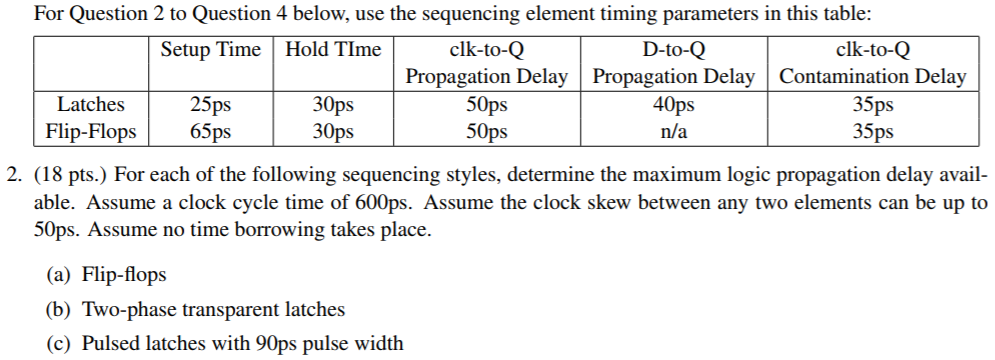

Question: For Question 2 to Question 4 below, use the sequencing element timing parameters in this table: clk-to-Q D-to-Q clk-to-Q Setup Time Hold TIme Propagation Delay

For Question 2 to Question 4 below, use the sequencing element timing parameters in this table: clk-to-Q D-to-Q clk-to-Q Setup Time Hold TIme Propagation Delay Propagation DelayContamination Delay Latches Flip-Flops 25ps 65ps 50ps 50ps 35ps 35ps 2. (18 pts.) For each of the following sequencing styles, determine the maximum logic propagation delay avail- able. Assume a clock cycle time of 600ps. Assume the clock skew between any two elements can be up to 50ps. Assume no time borrowing takes place. (a) Flip-flops (b) Two-phase transparent latches (c) Pulsed latches with 90ps pulse width For Question 2 to Question 4 below, use the sequencing element timing parameters in this table: clk-to-Q D-to-Q clk-to-Q Setup Time Hold TIme Propagation Delay Propagation DelayContamination Delay Latches Flip-Flops 25ps 65ps 50ps 50ps 35ps 35ps 2. (18 pts.) For each of the following sequencing styles, determine the maximum logic propagation delay avail- able. Assume a clock cycle time of 600ps. Assume the clock skew between any two elements can be up to 50ps. Assume no time borrowing takes place. (a) Flip-flops (b) Two-phase transparent latches (c) Pulsed latches with 90ps pulse width

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts