Question: For this problem we will be looking at a 6 4 6 4 SRAM ( i . e . , each wordline drives 6 4

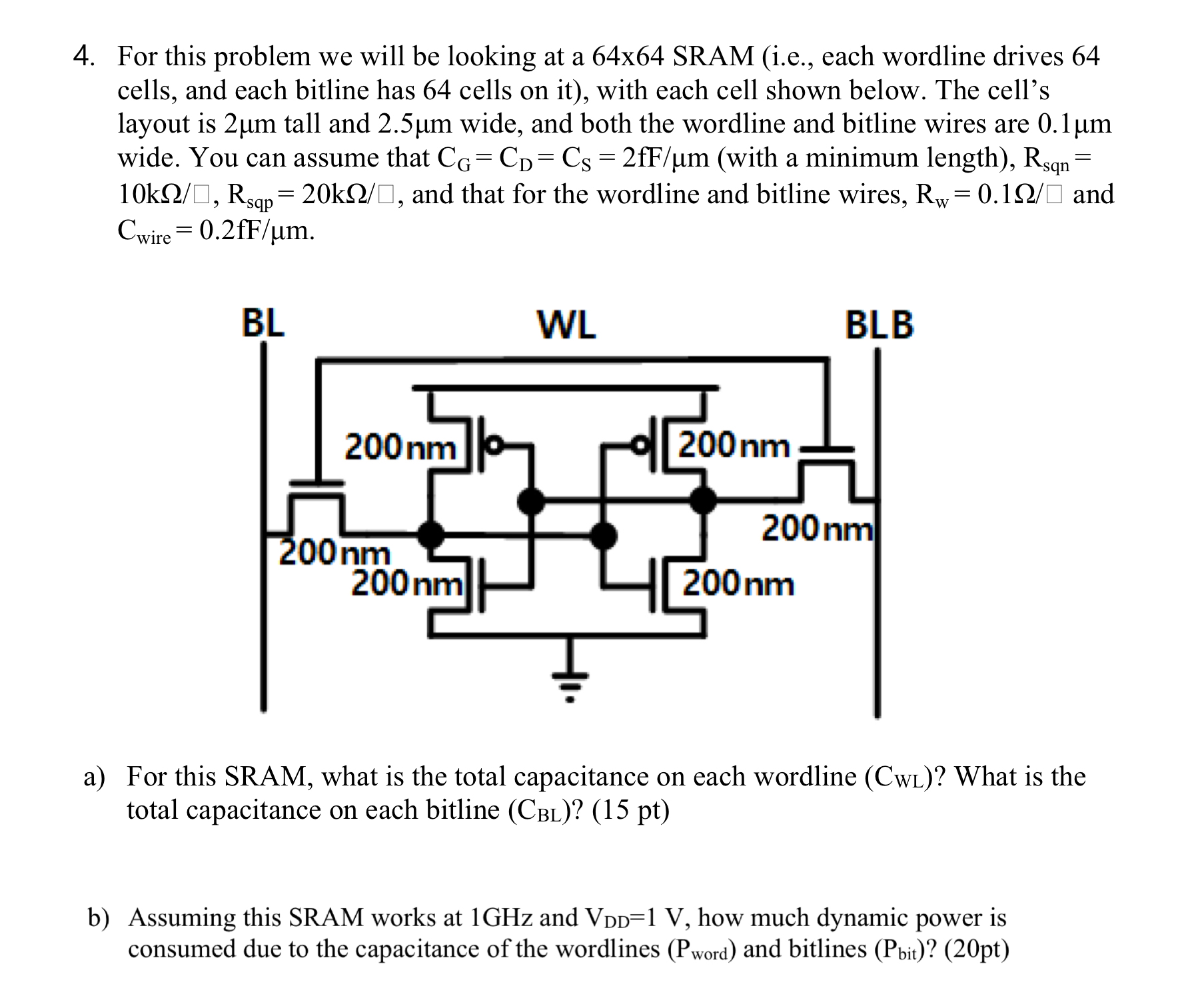

For this problem we will be looking at a SRAM ie each wordline drives cells, and each bitline has cells on it with each cell shown below. The cell's layout is tall and wide, and both the wordline and bitline wires are wide. You can assume that with a minimum length and that for the wordline and bitline wires, and

a For this SRAM, what is the total capacitance on each wordline What is the total capacitance on each bitline pt

b Assuming this SRAM works at GHz and how much dynamic power is consumed due to the capacitance of the wordlines and bitlines pt

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock