Question: FPGAs and Digital Design / Advanced Digital System Design Question 1 : Understand the merge sort algorithm which can be used to sort 8 numbers

FPGAs and Digital DesignAdvanced Digital System

Design

Question : Understand the merge sort algorithm which can be used to sort numbers in

ascending order. You are required to design a hardware representation for it using compare and

swap blocks as done in class for bubble sort algorithm.

Question : For the following equations design its equal hardware representation:

accacc

acc acc

out acc acc

where in and in are two bit inputs, out is a bit output, and acco and acc are two bit

internal registers.

Question : Design a bit counter such that counter pattern is or or using

Boolean logic and basic gates. You should first create a truth table for it create minterms or

maxterms and then use the SoP or PoS to create your final digital design.

Question : Implement the following Boolean expression using PAL and PLAs for a inputs,

and z

and

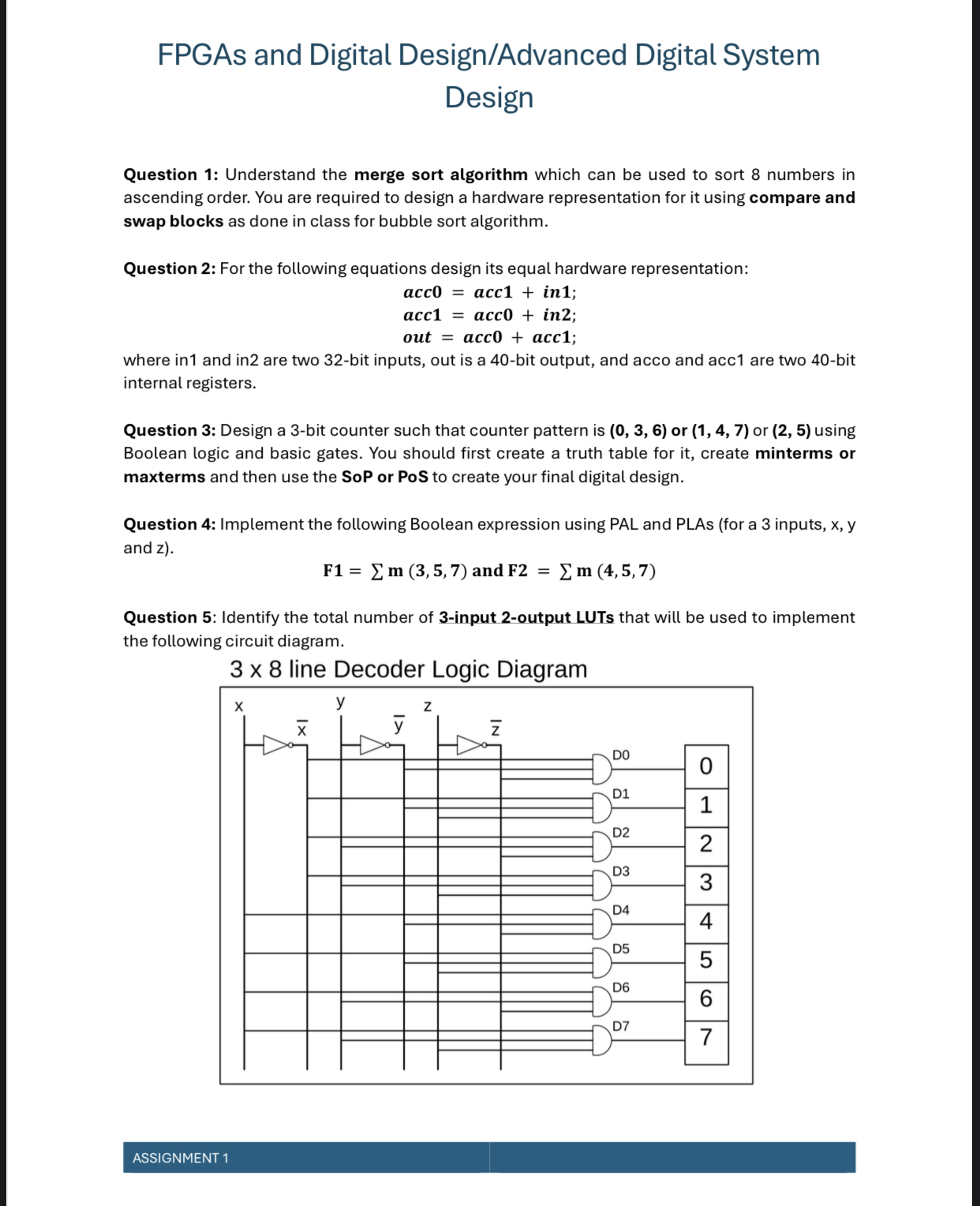

Question : Identify the total number of input output LUTs that will be used to implement

the following circuit diagram.

line Decoder Logic Diagram

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock