Question: give me the correct and detailed answer for this cache replacement : the question I provided of the High performance computer architecture course as follows

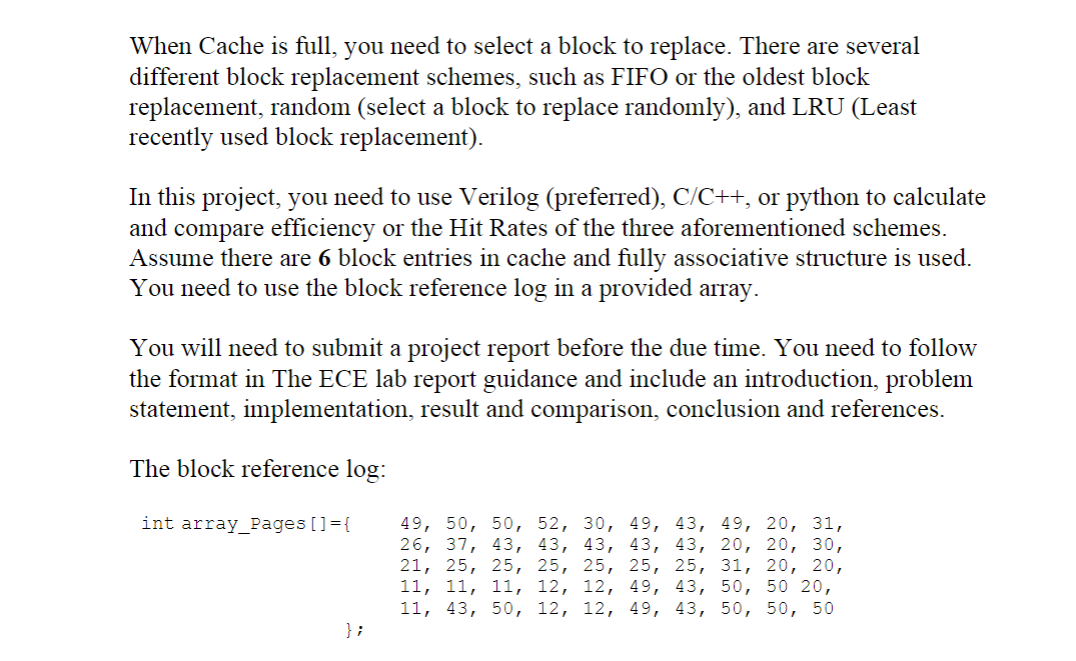

give me the correct and detailed answer for this cache replacement : the question I provided of the High performance computer architecture course as follows in the image :When Cache is full, you need to select a block to replace. There are several

different block replacement schemes, such as FIFO or the oldest block

replacement, random select a block to replace randomly and LRU Least

recently used block replacement

In this project, you need to use Verilog preferred or python to calculate

and compare efficiency or the Hit Rates of the three aforementioned schemes.

Assume there are block entries in cache and fully associative structure is used.

You need to use the block reference in a provided array.

You will need to submit a project report before the due time. You need to follow

the format in The ECE lab report guidance and include an introduction, problem

statement, implementation, result and comparison, conclusion and references.

The block reference log:

int ages

;

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock