Question: Given a chip having 3 different Sub-blocks, the first sub-block, contains from 500.000 CMOS Inverters, each inverter has 0.25pF silicon area, they operate at 3.3V

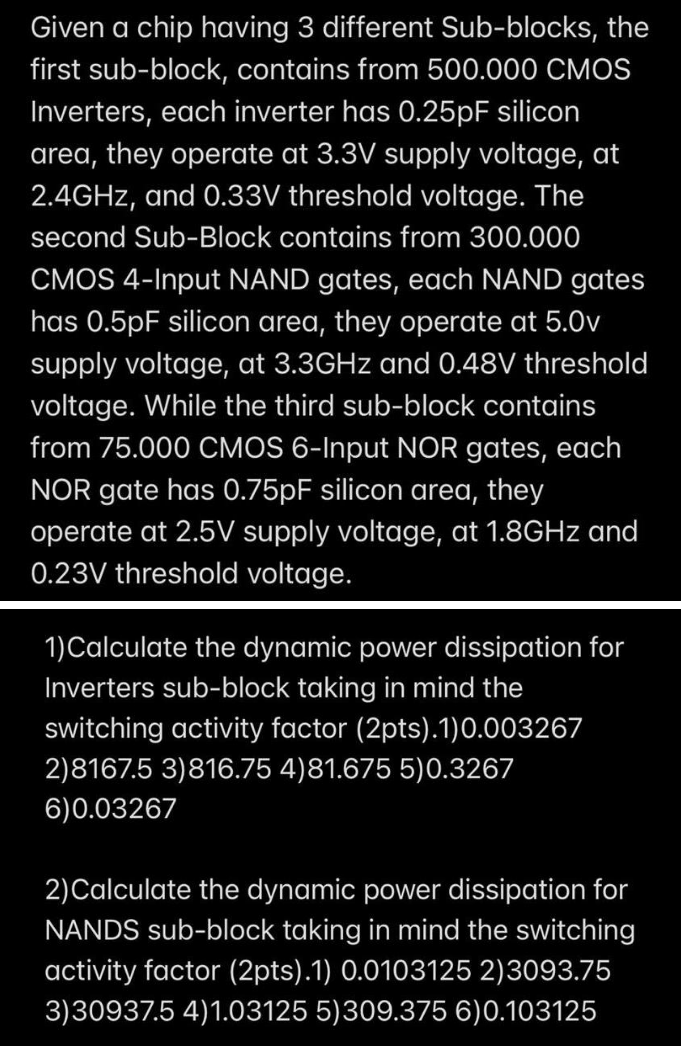

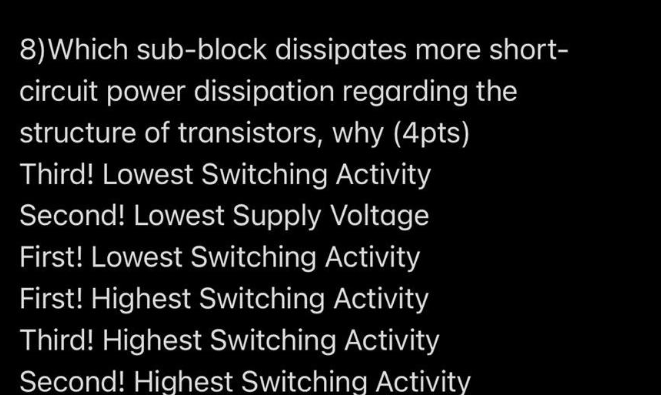

Given a chip having 3 different Sub-blocks, the first sub-block, contains from 500.000 CMOS Inverters, each inverter has 0.25pF silicon area, they operate at 3.3V supply voltage, at 2.4GHz, and 0.33V threshold voltage. The second Sub-Block contains from 300.000 CMOS 4-Input NAND gates, each NAND gates has 0.5pF silicon area, they operate at 5.Ov supply voltage, at 3.3GHz and 0.48V threshold voltage. While the third sub-block contains from 75.000 CMOS 6-Input NOR gates, each NOR gate has 0.75pF silicon area, they operate at 2.5V supply voltage, at 1.8GHz and 0.23V threshold voltage. 1) Calculate the dynamic power dissipation for Inverters sub-block taking in mind the switching activity factor (2pts).1)0.003267 2)8167.5 3)816.75 4)81.675 510.3267 610.03267 2)Calculate the dynamic power dissipation for NANDS sub-block taking in mind the switching activity factor (2pts).1) 0.0103125 2)3093.75 3)30937.5 4)1.03125 5)309.375 6)0.103125 8)Which sub-block dissipates more short- circuit power dissipation regarding the structure of transistors, why (4pts) Third! Lowest Switching Activity Second! Lowest Supply Voltage First! Lowest Switching Activity First! Highest Switching Activity Third! Highest Switching Activity Second! Highest Switching Activity

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts