Question: Given this processor hardware design, suppose that the following control state is the limiting factor in determining the maximum clock speed. Given that the propagation

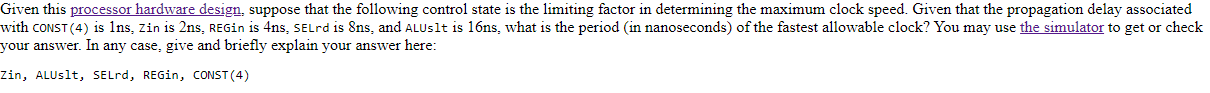

Given this processor hardware design, suppose that the following control state is the limiting factor in determining the maximum clock speed. Given that the propagation delay associated with CONST(4) is lns, Zin is 2ns. REGin is 4ns, SELrd is Sns, and ALUslt is 16ns, what is the period in nanoseconds) of the fastest allowable clock? You may use the simulator to get or check your answer. In any case, give and briefly explain your answer here: Zin, ALUslt, SELrd, REGin, CONST (4) Given this processor hardware design, suppose that the following control state is the limiting factor in determining the maximum clock speed. Given that the propagation delay associated with CONST(4) is lns, Zin is 2ns. REGin is 4ns, SELrd is Sns, and ALUslt is 16ns, what is the period in nanoseconds) of the fastest allowable clock? You may use the simulator to get or check your answer. In any case, give and briefly explain your answer here: Zin, ALUslt, SELrd, REGin, CONST (4)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts