Question: Hello Chegg user, this is my first question ever on this site. If this is not the correct format, then I apologize. Anyway, I need

Hello Chegg user, this is my first question ever on this site. If this is not the correct format, then I apologize. Anyway, I need help with this question as this is something I'm not too familiar with. Any help on this question is greatly appreciated, even if it is only for one of the parts. Thanks for your help!

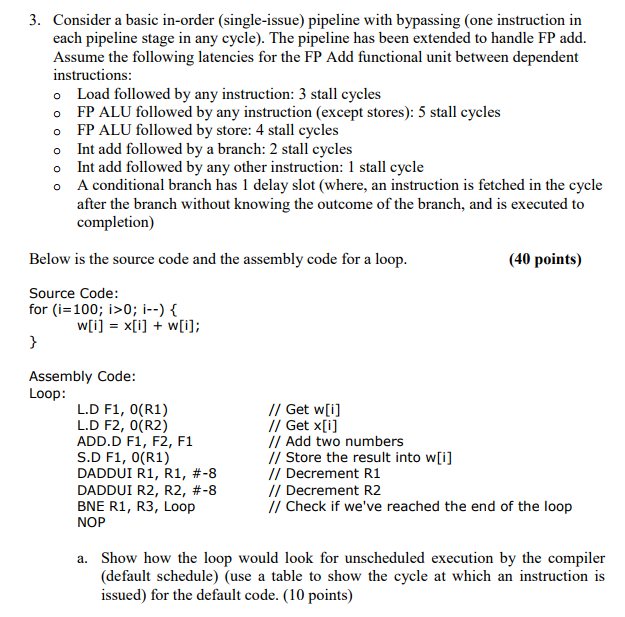

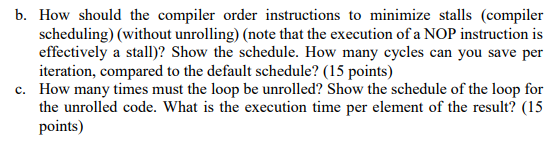

3. Consider a basic in-order (single-issue) pipeline with bypassing (one instruction in each pipeline stage in any cycle). The pipeline has been extended to handle FP add. Assume the following latencies for the FP Add functional unit between dependent nstructions o Load followed by any instruction: 3 stall cycles o FP ALU followed by any instruction (except stores): 5 stall cycles o FP ALU followed by store: 4 stall cycles o Int add followed by a branch: 2 stall cycles o Int add followed by any other instruction: 1 stall cycle o A conditional branch has 1 delay slot (where, an instruction is fetched in the cycle after the branch without knowing the outcome of the branch, and is executed to completion) Below is the source code and the assembly code for a loop (40 points) Source Code: for (i-100; i>0; i--)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts