Question: hello, I need help in this question please, step by step with explanations, I really need help to understand this question. Thank you. Q1. We

hello, I need help in this question please, step by step with explanations, I really need help to understand this question. Thank you.

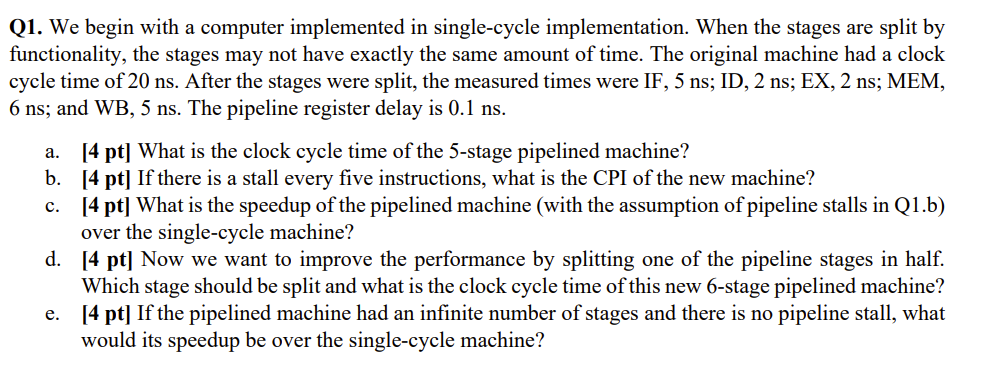

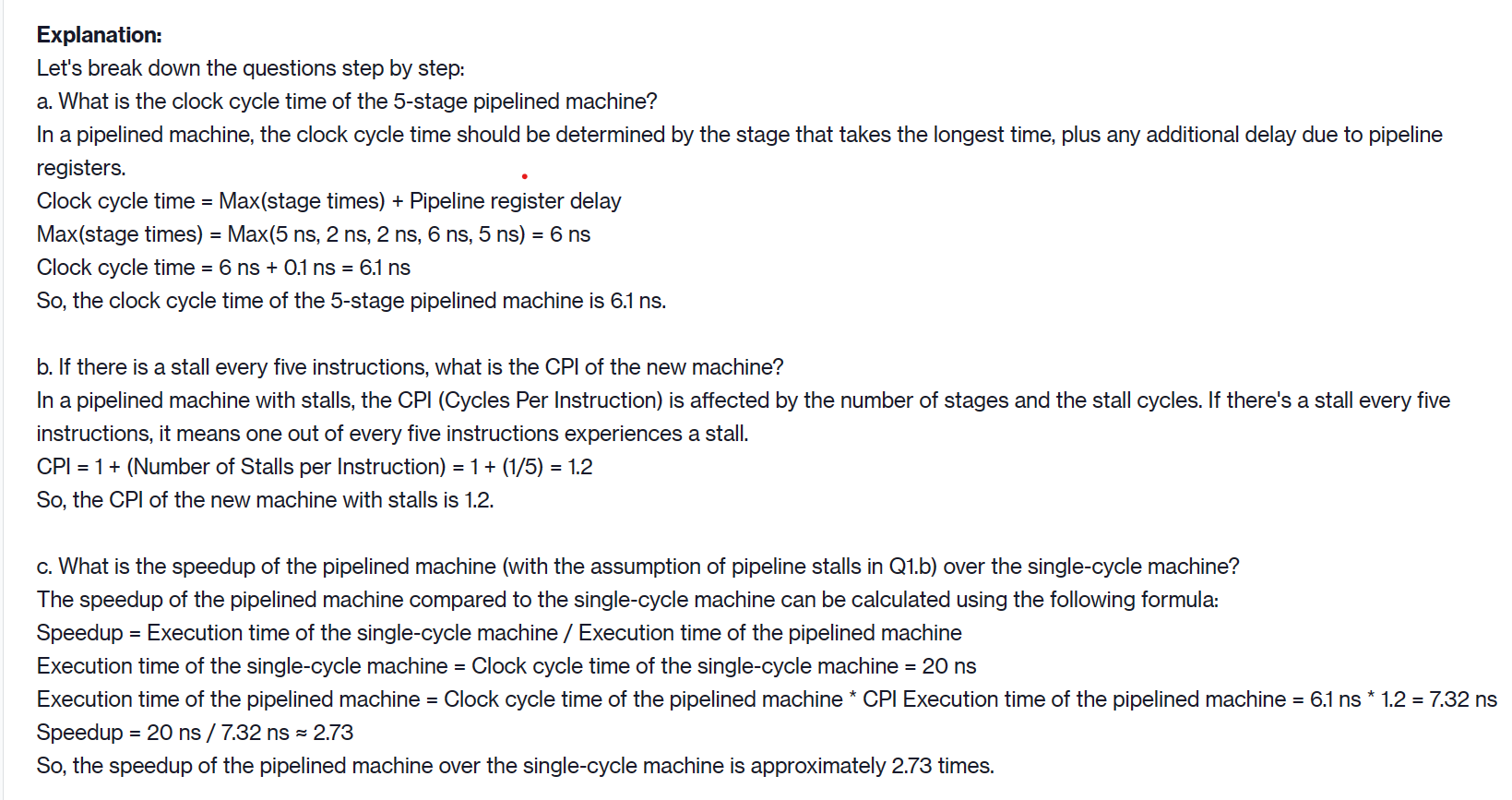

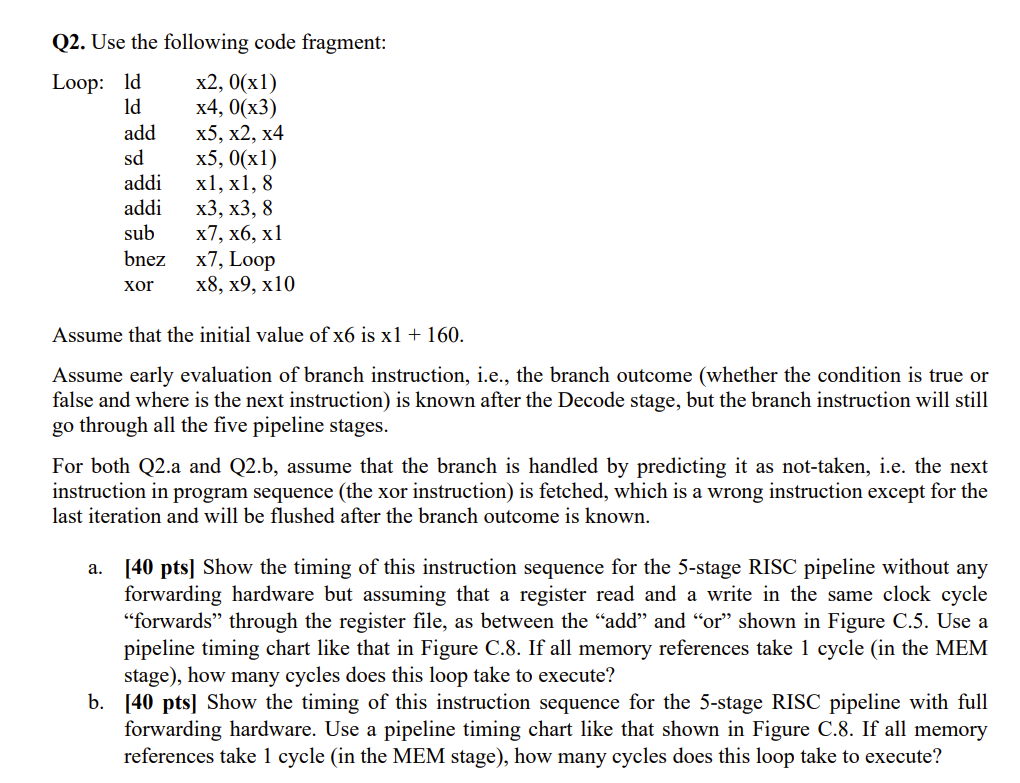

Q1. We begin with a computer implemented in single-cycle implementation. When the stages are split by functionality, the stages may not have exactly the same amount of time. The original machine had a clock cycle time of 20 ns. After the stages were split, the measured times were IF, 5 ns; ID, 2 ns; EX, 2 ns; MEM, 6 ns; and WB, 5 ns. The pipeline register delay is 0.1 ns. a. [4 pt] What is the clock cycle time of the 5-stage pipelined machine? b. [4 pt] If there is a stall every five instructions, what is the CPI of the new machine? c. [4 pt] What is the speedup of the pipelined machine (with the assumption of pipeline stalls in Q1.b) over the single-cycle machine? d. [4 pt] Now we want to improve the performance by splitting one of the pipeline stages in half. Which stage should be split and what is the clock cycle time of this new 6-stage pipelined machine? e. [4 pt] If the pipelined machine had an infinite number of stages and there is no pipeline stall, what would its speedup be over the single-cycle machine?Explanation: Let's break down the questions step by step: a. What is the clock cycle time of the 5-stage pipelined machine? In a pipelined machine, the clock cycle time should be determined by the stage that takes the longest time, plus any additional delay due to pipeline registers. Clock cycle time = Max(stage times) + Pipeline register delay Max(stage times) = Max(5 ns, 2 ns, 2 ns, 6 ns, 5 ns) = 6 ns Clock cycle time = 6 ns + 0.1 ns = 6.1 ns So, the clock cycle time of the 5-stage pipelined machine is 6.1 ns. b. If there is a stall every five instructions, what is the CPI of the new machine? In a pipelined machine with stalls, the CPI (Cycles Per Instruction) is affected by the number of stages and the stall cycles. If there's a stall every five instructions, it means one out of every five instructions experiences a stall. CPI = 1 + (Number of Stalls per Instruction) = 1 + (1/5) = 1.2 So, the CPI of the new machine with stalls is 1.2. c. What is the speedup of the pipelined machine (with the assumption of pipeline stalls in Q1.b) over the single-cycle machine? The speedup of the pipelined machine compared to the single-cycle machine can be calculated using the following formula: Speedup = Execution time of the single-cycle machine / Execution time of the pipelined machine Execution time of the single-cycle machine = Clock cycle time of the single-cycle machine = 20 ns Execution time of the pipelined machine = Clock cycle time of the pipelined machine * CPI Execution time of the pipelined machine = 6.1 ns * 1.2 = 7.32 ns Speedup = 20 ns / 7.32 ns = 2.73 So, the speedup of the pipelined machine over the single-cycle machine is approximately 2.73 times.Q2. Use the following code fragment: Loop: ld x2, 0(xl) ld x4, 0(x3) add x5, x2, x4 sd x5, 0(x1) addi x], x], 8 addi x3, x3, 8 sub xT, x6, x] bnez xT, Loop xor x8, x9, x10 Assume that the initial value of x6 is x] + 160. Assume early evaluation of branch instruction, i.e., the branch outcome (whether the condition is true or false and where is the next instruction) is known after the Decode stage, but the branch instruction will still go through all the ve pipeline stages. For both Q2.a and Q2.b, assume that the branch is handled by predicting it as not-taken, i.e. the next instruction in program sequence (the xor instruction) is fetched, which is a wrong instruction except for the last iteration and will be flushed after the branch outcome is known. a. [40 pts] Show the timing of this instruction sequence for the 5-stage RISC pipeline without any forwarding hardware but assuming that a register read and a write in the same clock cycle \"forwards\" through the register le, as between the \"add\" and \"or\" shown in Figure C.5. Use a pipeline timing chart like that in Figure C.8. If all memory references take 1 cycle (in the MEM stage), how many cycles does this loop take to execute?I b. [40 pts] Show the timing of this instruction sequence for the 5-stage RISC pipeline with lll forwarding hardware. Use a pipeline timing chart like that shown in Figure CS. If all memory references take 1 cycle ( in the MEM stage), how many cycles does this loop take to execute?I d. Now we want to improve the performance by splitting one of the pipeline stages in half. Which stage should be split, and what is the clock cycle time of this new 6-stage pipelined machine? To improve performance, we should split the stage that takes the longest time because this will reduce the clock cycle time. In this case, the "MEM" stage takes the longest time (6 ns), so we should split it in half to reduce the stage time. New stage times: . IF: 5 ns . ID: 2 ns . EX: 2 ns . MEM (original): 6 ns . MEM (split): 3 ns (half of the original time) . WB: 5 ns Clock cycle time = Max(stage times) + Pipeline register delay Max(stage times) = Max(5 ns, 2 ns, 2 ns, 3 ns, 3 ns, 5 ns) = 5 ns Clock cycle time = 5 ns + 0.1 ns = 5.1 ns So, the clock cycle time of the new 6-stage pipelined machine with a split "MEM" stage is 5.1 ns. e. If the pipelined machine had an infinite number of stages and there is no pipeline stall, what would its speedup be over the single-cycle machine? In an ideal scenario with an infinite number of pipeline stages and no pipeline stalls, the speedup can be calculated as follows: Speedup = Execution time of the single-cycle machine / Execution time of the pipelined machine Execution time of the single-cycle machine = Clock cycle time of the single-cycle machine = 20 ns Execution time of the pipelined machine with infinite stages and no stalls can be approximated as:Max(stage times) = Max(5 ns, 2 ns, 2 ns, 3 ns, 3 ns, 5 ns) = 5 ns Clock cycle time = 5 ns + 0.1 ns = 5.1 ns So, the clock cycle time of the new 6-stage pipelined machine with a split "MEM" stage is 5.1 ns. e. If the pipelined machine had an infinite number of stages and there is no pipeline stall, what would its speedup be over the single-cycle machine? In an ideal scenario with an infinite number of pipeline stages and no pipeline stalls, the speedup can be calculated as follows: Speedup = Execution time of the single-cycle machine / Execution time of the pipelined machine Execution time of the single-cycle machine = Clock cycle time of the single-cycle machine = 20 ns Execution time of the pipelined machine with infinite stages and no stalls can be approximated as: Execution time of the pipelined machine = (Max(stage times) + Pipeline register delay) * Number of Stages Max(stage times) = 6 ns (from part a) Execution time of the pipelined machine = (6 ns + 0.1 ns) * co = 6.1 ns * co = 00 In this idealized scenario, the execution time of the pipelined machine approaches infinity. As a result, the speedup would be: Speedup = 20 ns / 0. = 0 (approaching zero) In practical terms, with an infinite number of stages and no stalls, the pipelined machine would execute instructions much faster than the single-cycle machine, but this theoretical speedup calculation becomes impractical

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts