Question: Hi this is a memory problem from my computer architecture class. Question 4 Memory Hierarchy A computer system has a 128 byte cache. It uses

Hi this is a memory problem from my computer architecture class.

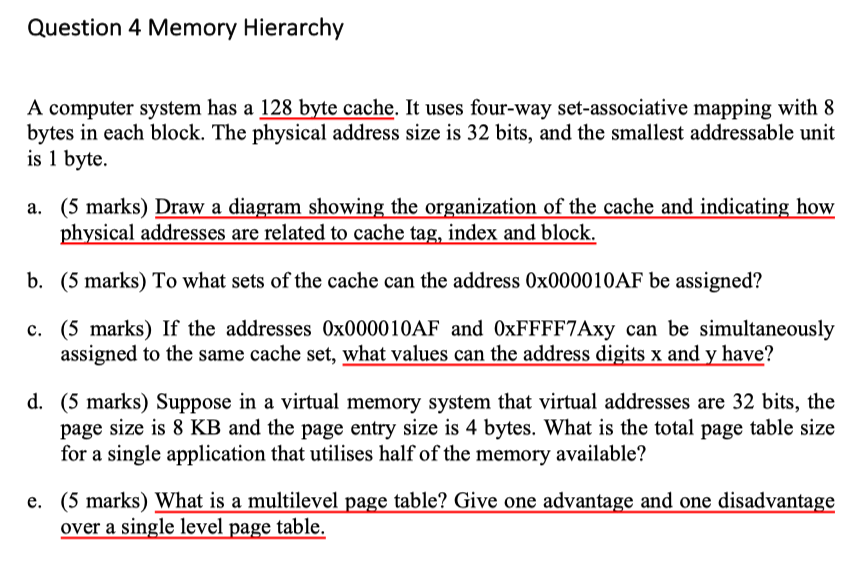

Question 4 Memory Hierarchy A computer system has a 128 byte cache. It uses four-way set-associative mapping with 8 bytes in each block. The physical address size is 32 bits, and the smallest addressable unit is 1 byte. a. (5 marks) Draw a diagram showing the orzanization of the cache and indicating how. physical addresses are related to cache tag, index and block. (5 marks) To what sets of the cache can the address 0x000010AF be assigned? assigned to the same cache set, what values can the address digits x and y have? page size is 8 KB and the page entry size is 4 bytes. What is the total page table size b. c. (5 marks) If the addresses 0x000010AF and 0xFFFF7Axy can be simultaneously d. (5 marks) Suppose in a virtual memory system that virtual addresses are 32 bits, the for a single application that utilises half of the memory available? e. (5 marks) What is a multilevel page table? Give one advantage and one disadvantage over a single level page table

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts