Question: Homework # 9 1 . Convert by adding external gates: a . A JK flip - flop into a D flip - flop b

Homework #

Convert by adding external gates:

a A JK flipflop into a D flipflop

b A JK flipflop into a T flipflop

c An T flip flop into an SR flip flop.

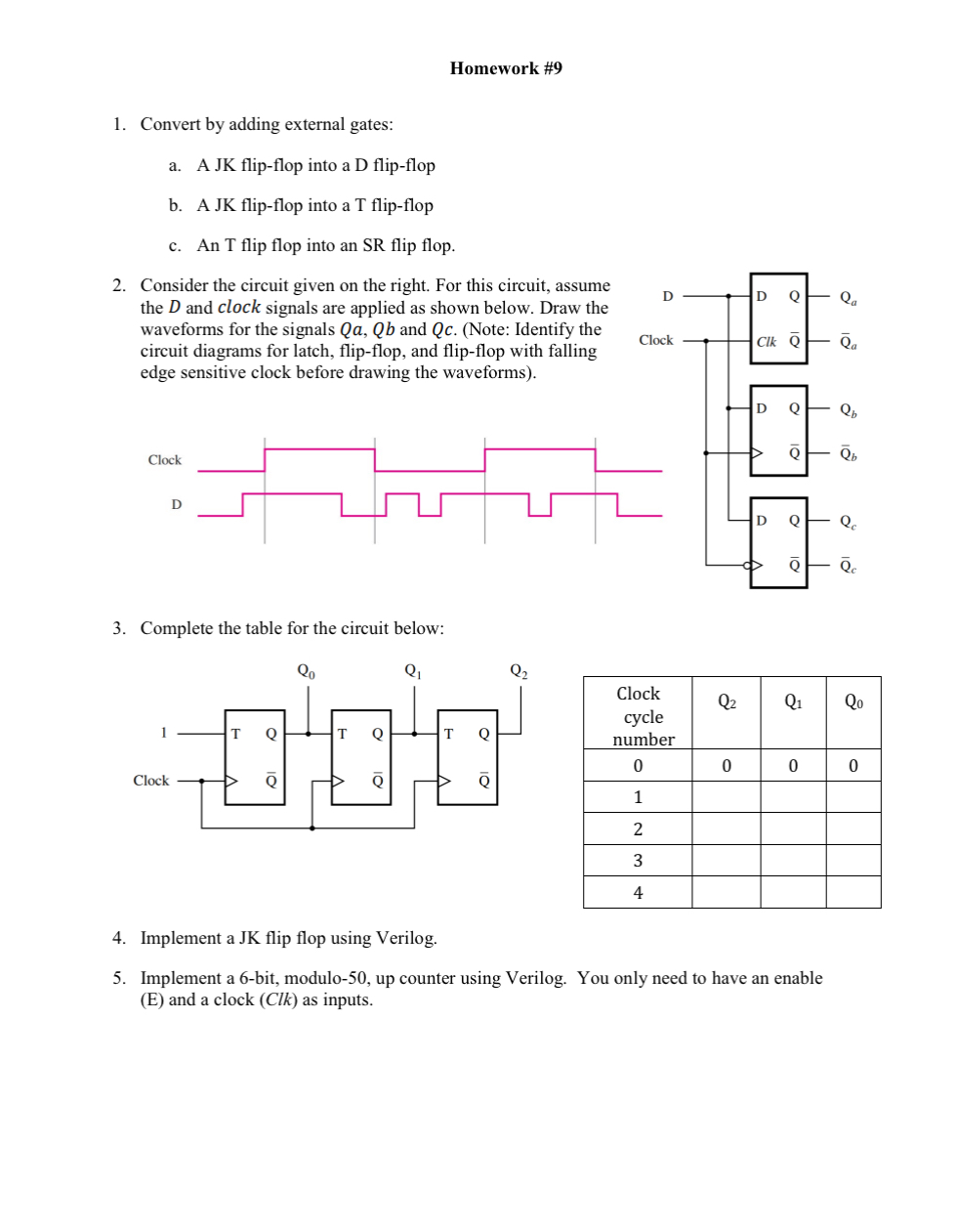

Consider the circuit given on the right. For this circuit, assume the D and clock signals are applied as shown below. Draw the waveforms for the signals Q a Q b and Q c Note: Identify the circuit diagrams for latch, flipflop, and flipflop with falling

edge sensitive clock before drawing the waveforms

Complete the table for the circuit below:

Implement a JK flip flop using Verilog.

Implement a bit, modulo up counter using Verilog. You only need to have an enable E and a clock Clk as inputs.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock