Question: how the step-by-step execution using the tables below -EXCEL- (Tomasulo) and (HW-based speculation). What are the numbers of cycles to finish the first two iterations

how the step-by-step execution using the tables below -EXCEL- (Tomasulo) and (HW-based speculation).

What are the numbers of cycles to finish the first two iterations using the above two approached? Count the cycles from the first instruction being issued to the last instruction that finishes.

Consider the code below.]

Loop:

fld f0, 0(x1)

fmul.d f4, f0, f2

fsd f4, 0(x1)

fsub.d f4, f10, f14

addi x1, x1, 8

bne x1, x2, Loop // branches if x1 /= x2

Assume the following latencies:

(a) fld/fsd: 1 cycle

(b) fsub.d: 2 cycles

(c) addi/bne: 1 cycle

(d) fmul.d: 6 cycles

Assume that branches are predicted as taken. Execute the above code for two iterations using

1 Tomasulos approach

2 Hardware-based speculation

Tomasulo's worksheet

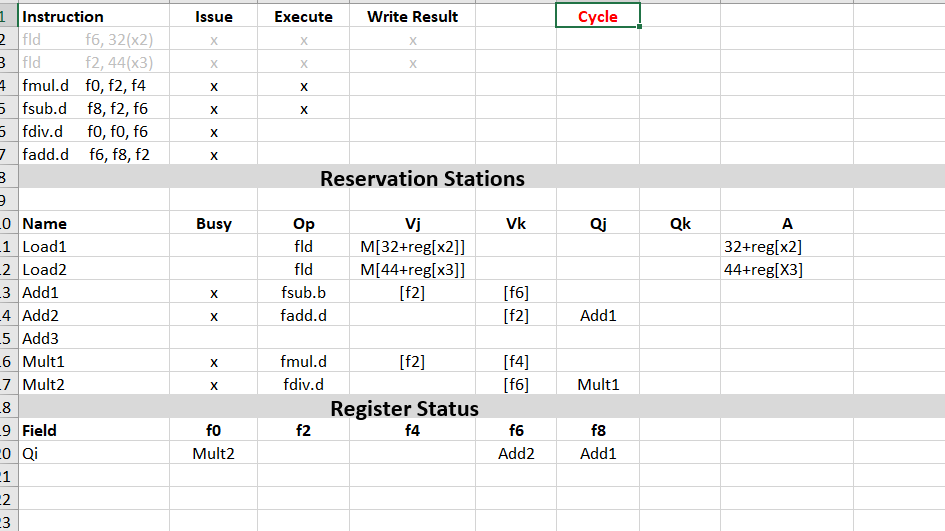

Instruction Write Result Cycle Issue Execute fld fld f6, 32(x2) f2, 44(x3 4 fmul.d fo, f2, f4 fsub.d f8, f2, f6 5 fdiv.d fo, fo, f6 7 fadd.d f6, f8, f2 Reservation Stations 0 Name 1 Load1 2 Load2 3 Add1 4 Add2 5 Add3 6 Mult1 7 Mult2 Busy Op fld fld fsub.b fadd.d Qk MI32+reg[x2]] M[44+reg[x3]] 32+reg[x2] 44+reg[X3 [f6] f2 Add1 fmul.d fdiv.d f4 [f6 Mult1 Register Status 9 Field 0 Qi fo Mult2 f2 f4 f8 Add1 f6 Add2 Instruction Write Result Cycle Issue Execute fld fld f6, 32(x2) f2, 44(x3 4 fmul.d fo, f2, f4 fsub.d f8, f2, f6 5 fdiv.d fo, fo, f6 7 fadd.d f6, f8, f2 Reservation Stations 0 Name 1 Load1 2 Load2 3 Add1 4 Add2 5 Add3 6 Mult1 7 Mult2 Busy Op fld fld fsub.b fadd.d Qk MI32+reg[x2]] M[44+reg[x3]] 32+reg[x2] 44+reg[X3 [f6] f2 Add1 fmul.d fdiv.d f4 [f6 Mult1 Register Status 9 Field 0 Qi fo Mult2 f2 f4 f8 Add1 f6 Add2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts