Question: I am not too sure how to do state tables / diagrams , K - maps and Block diagrams in relation to the following systems:

I am not too sure how to do state tablesdiagrams Kmaps and Block diagrams in relation to the following systems:

a Draw a State stable for the Sequence Recogniser

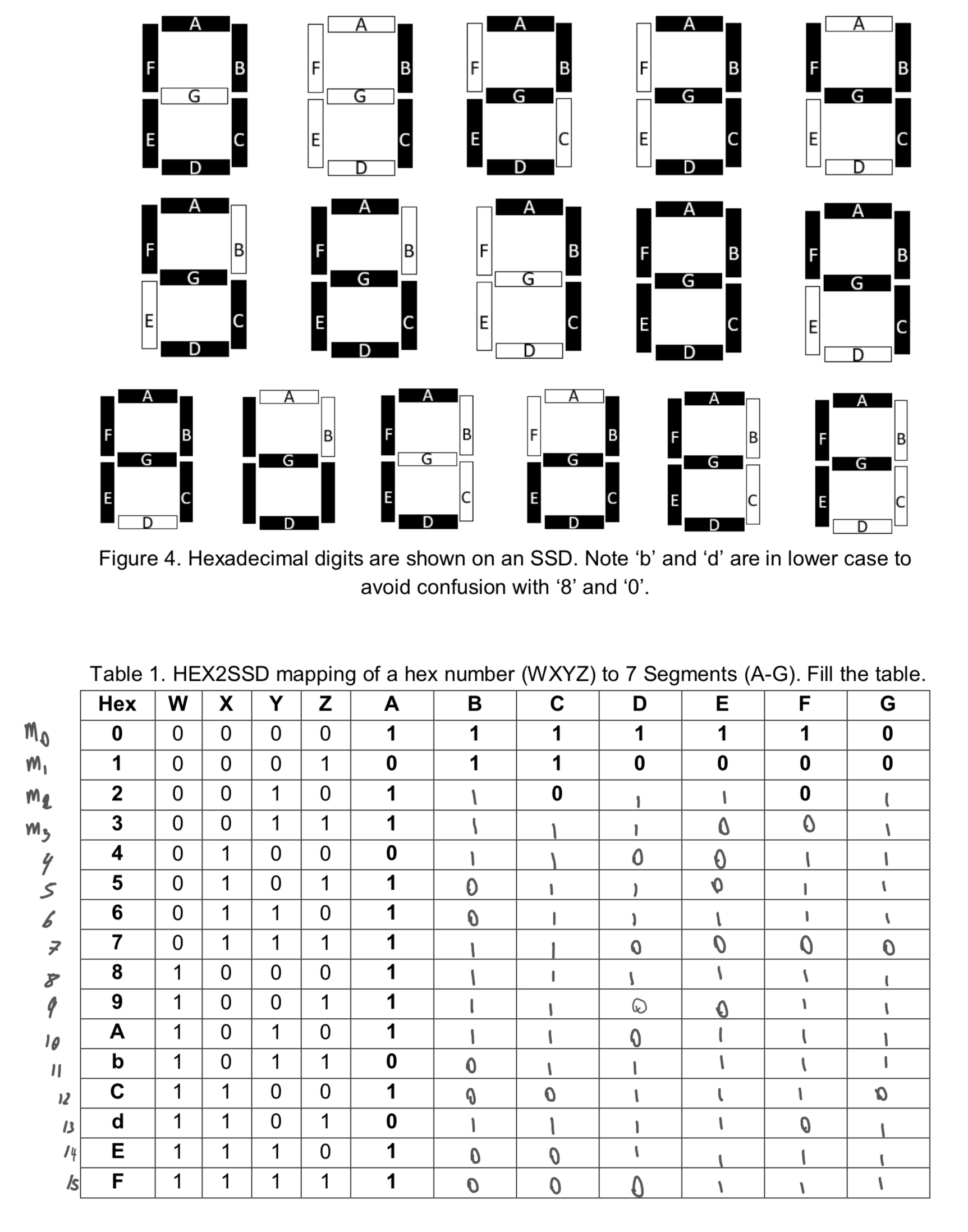

b Draw Kmaps for : Sequence Recogniser and Pattern displays, Decoder, BCD Counter

c Draw Block Diagrams for: sequence recogniser, decoder, multiplexer to BCD counter, clock divider, and pattern display.

FOR MORE CONTEXT:

The aim is to create a Smart MultiPurpose Clock using the OMDAZZ Altera Intel FPGA Experimenter Board.

System Initialisation when powered up or reset, it should enter a locked mode. The segment displays SSD should show EEEE and all LEDs should remain off.

Password Recogniser the binary sequence password which is If the digit is even including zero it will be represented by a and if it is odd, it will be represented by a Each button entry must only trigger one change in state ie holding the button does not enter multiple digits and you can assign two pushbuttons for and respectively.

Examples of converting to binary sequence:

has OEOE pattern and would become OOdd, EEven

EEOE would become

EEOO would become

Also, the progress of the sequence recogniser should be displayed on the seven segment displays. Example with which has a password :

Initial SSD output E E E E

Input correct st number E E E

Input correct nd number E E

Input incorrect rd number E E E E

Any incorrect inputs MUST reset the system to the starting state. For example, with a passcode of currently at the state E the system should return to EEEE if the next input is a Once the correct sequence has been entered, the system should exit the locked mode and enter a Clock Mode. When your system is in Clock Mode, the LEDs should all light up and remain lit.

Clock Mode where the SSD function as a clock. The lowest unit of the clock should be onehundredth of a second. Thus the clock should increment every hundredth of a second. When the clock equals the four digits, the system should reset the clock to zero and continue to count.

Example with :

At time t clock is less than last four digits

At time t clock is same as last four digits

At time t clock resets

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock