Question: i. Derive the state diagram (Mealy design) for a sequence counter which detect and count the sequence of 101101 (without overlapping). (06 Marks) The senior

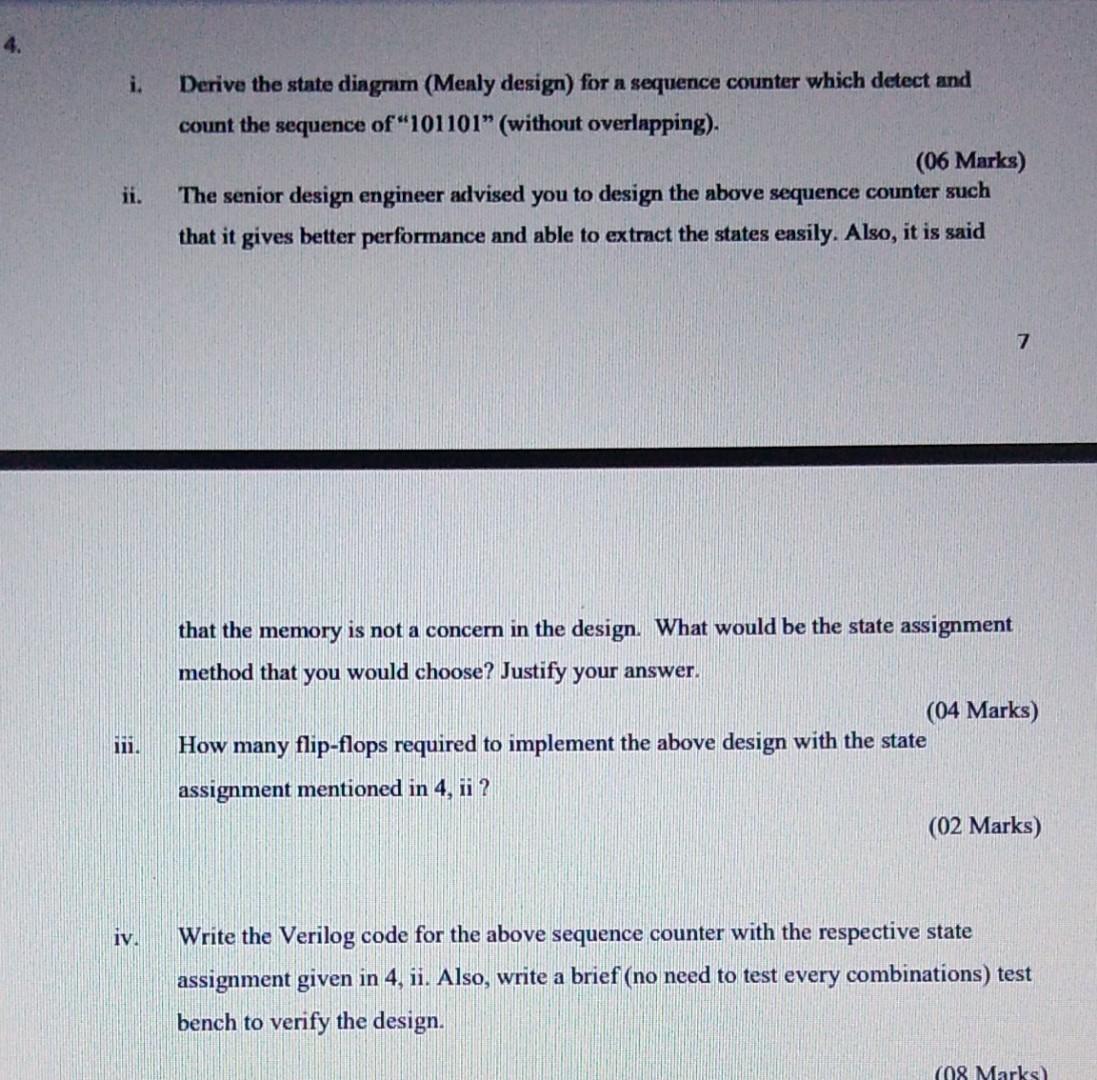

i. Derive the state diagram (Mealy design) for a sequence counter which detect and count the sequence of 101101" (without overlapping). (06 Marks) The senior design engineer advised you to design the above sequence counter such that it gives better performance and able to extract the states easily. Also, it is said ii. 7 that the memory is not a concern in the design. What would be the state assignment method that you would choose? Justify your answer. (04 Marks) How many flip-flops required to implement the above design with the state assignment mentioned in 4, ii ? (02 Marks) iii. IV. Write the Verilog code for the above sequence counter with the respective state assignment given in 4, ii. Also, write a brief (no need to test every combinations) test bench to verify the design. (08 Marks)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts