Question: I have a zero-ones test in the test bench; can someone show me a checkerboard test, march test, and a sliding diagonal/walking ones test? module

I have a zero-ones test in the test bench; can someone show me a checkerboard test, march test, and a sliding diagonal/walking ones test?

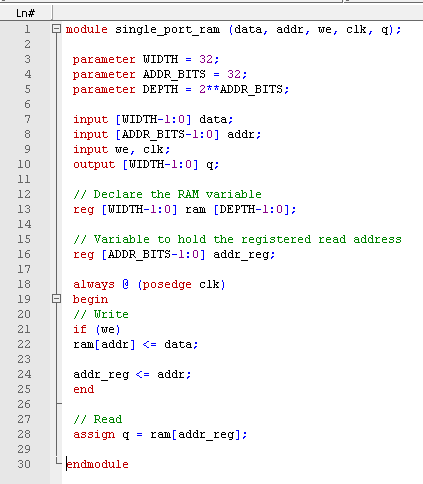

![= 32; parameter DEPTH = 2**ADDRBITS; - - input [WIDTH-1:0] data; input](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f69151d14c6_08966f691517ae5e.jpg)

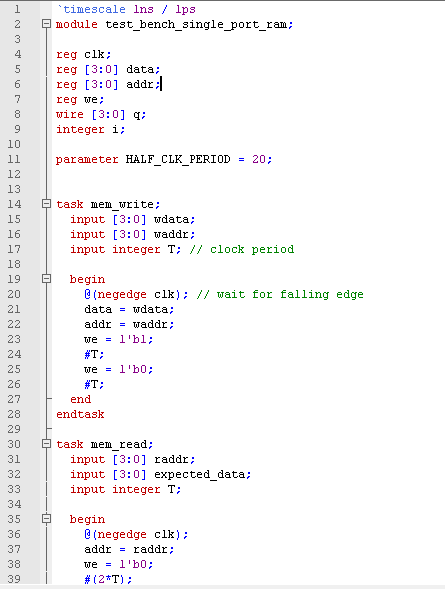

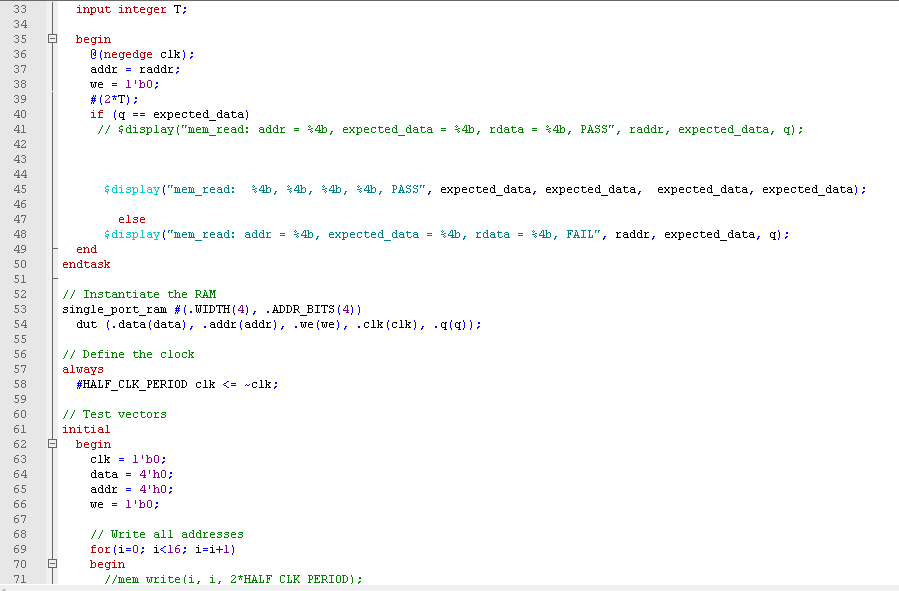

module single_port_ram (data, addr, we, clk,q parameter WIDTH = 32; parameter ADDRBITS = 32; parameter DEPTH = 2**ADDRBITS; - - input [WIDTH-1:0] data; input [ADDR BITS-1:0] addr; input we, clk; output [WIDTH-1:0] q: 12 13 14 15 16 17 / Declare the RAM variable reg WIDTH-1:0] ram [DEPTH-1:0]: // Variable to hold the registered read addresS reg [ADDR BITS-1:0] addr reg; always (posedge clk) begin // Write if (we) ram[addr] data; 20 21 23 24 25 26 27 addrreg = addr ; end - // Read assign 4 = ram[addr-reg]; 30 ndmodule module single_port_ram (data, addr, we, clk,q parameter WIDTH = 32; parameter ADDRBITS = 32; parameter DEPTH = 2**ADDRBITS; - - input [WIDTH-1:0] data; input [ADDR BITS-1:0] addr; input we, clk; output [WIDTH-1:0] q: 12 13 14 15 16 17 / Declare the RAM variable reg WIDTH-1:0] ram [DEPTH-1:0]: // Variable to hold the registered read addresS reg [ADDR BITS-1:0] addr reg; always (posedge clk) begin // Write if (we) ram[addr] data; 20 21 23 24 25 26 27 addrreg = addr ; end - // Read assign 4 = ram[addr-reg]; 30 ndmodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts