Question: I know the question is long, but please answer both parts it would really help. Thanks. I can also provide extra unfo if needed. Whats

I know the question is long, but please answer both parts it would really help. Thanks. I can also provide extra unfo if needed.

Whats the last non-zero digit of your ID? 6

Whats that number times 4? 24 Thats your tax percentage.

Practice problem

For the example, Im using 18% penalty (which I realize isnt 4 times anyones ID digit) and 3.5GHz core speed. Youll see in row 2 that I got 1.48E8 by adding 18% to the original IC for math instructions. The CPI doesnt change, but the total cycles does. I calculated all the fields in yellow as if they were blank when I started.

| Multicore penalty | 18 | % |

| Core speed | 3.5 | GHz |

| Math IC | CPI for Math | Cycles across Math IC | L/S IC | CPI for LS | Cycles across L/W IC | Branch IC | CPI for Branch | Cycles across Branch IC | Total Cycles | Execution Time | Speedup | |

| Original IC for 1 core | 1.25E+08 | 6.6 | 8.25E+08 | 1.54E+08 | 7.1 | 1.09E+09 | 2.36E+08 | 2.7 | 6.37E+08 | 2.56E+09 | 0.7302 | 1.00 |

| New IC with "tax" | 1.48E+08 | 6.6 | 9.74E+08 | 1.82E+08 | 7.1 | 1.29E+09 | 2.78E+08 | 2.7 | 7.52E+08 | 3.02E+09 | 0.8616 | 0.85 |

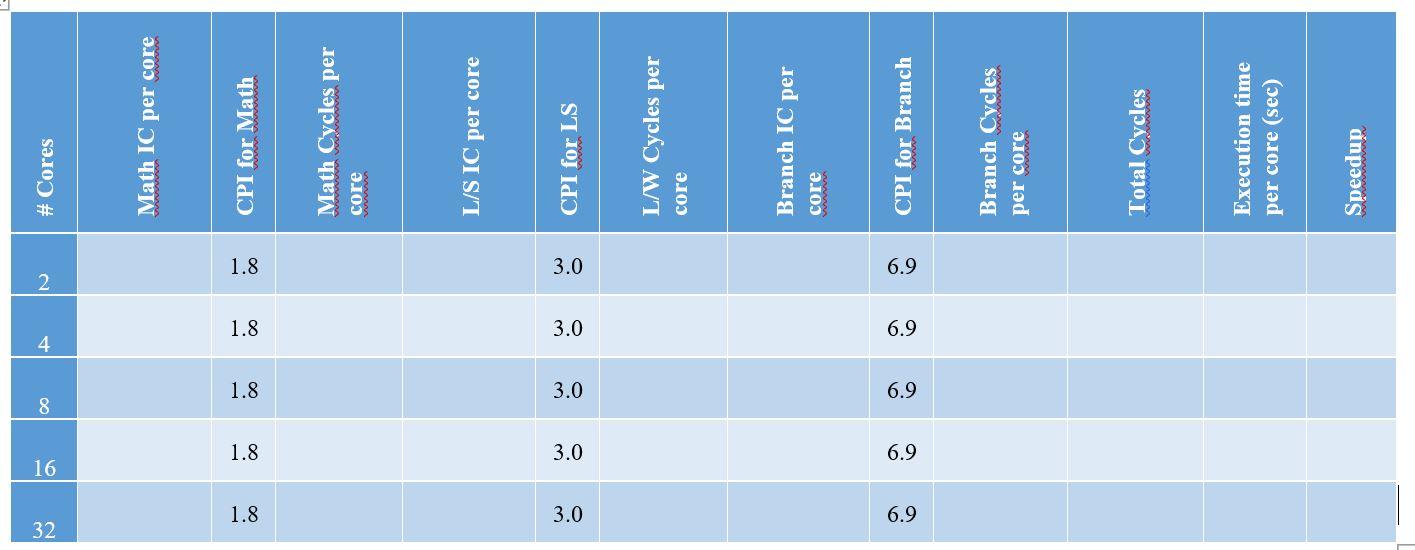

Now its your turn. Use the penalty (the tax) you calculated above from your student ID. Fill it in here again. The processor speed is given to you. Then fill in the missing fields in the table. What you are calculating is the extra instructions and thus the extra cycles and time required from deciding to add code to handle coordination. Next well spread your program with extra instructions across multiple cores.

| Multicore penalty | % | |

| Core speed | 3.7 | GHz |

| Math IC | CPI for Math | Cycles across Math IC | L/S IC | CPI for LS | Cycles across L/W IC | Branch IC | CPI for Branch | Cycles across Branch IC | Total Cycles | Execution Time | Speedup | |

| Original IC for 1 core | 1.09E+08 | 1.8 | 1.75E+08 | 3.0 | 2.20E+08 | 6.9 | 1.00 | |||||

| New IC with "tax" |

| 1.8 |

|

| 3.0 |

|

| 6.9 |

|

|

|

|

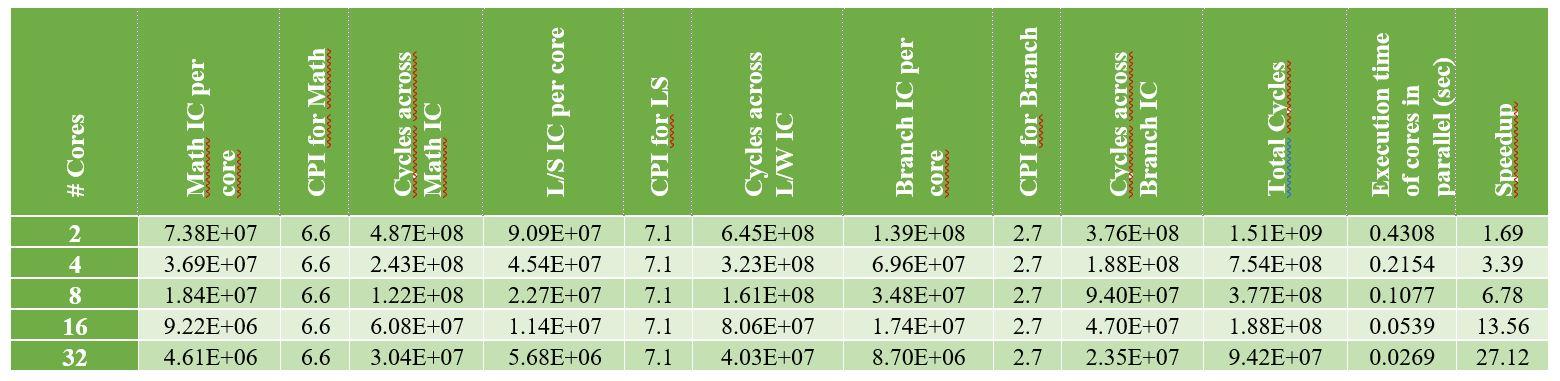

Math IC per CPI for Math Cycles across Math IC LIS IC per core CPI for LS Cycles across L/WIC Branch IC per CPI for Branch Cycles across Branch IC Total Cycles Execution time of cores in parallel (sec) core core Speedup 7.1 2.7 SON # Cores 7.1 2.7 7.38E+07 3.69E+07 1.84E+07 9.22E+06 4.61E+06 6.6 6.6 6.6 6.6 6.6 4.87E+08 2.43E+08 1.22E+08 6.08E+07 3.04E+07 9.09E+07 4.54E+07 2.27E+07 1.14E+07 5.68E+06 7.1 7.1 7.1 6.45E+08 3.23E+08 1.61E+08 8.06E+07 4.03E+07 1.39E+08 6.96E+07 3.48E+07 1.74E+07 8.70E+06 2.7 2.7 2.7 3.76E+08 1.88E+08 9.40E+07 4.70E+07 2.35E+07 1.51E+09 7.54E+08 3.77E+08 1.88E+08 9.42E+07 0.4308 0.2154 0.1077 0.0539 0.0269 1.69 3.39 6.78 13.56 27.12 32 16 8 4 N # Cores Math IC per core 1.8 CPI for Math Math Cycles per core LIS IC per core 3.0 3.0 3.0 3.0 30 CPI for LS L/W Cycles per core Branch IC per core 6.9 6.9 6.9 6.9 6.9 CPI for Branch Branch Cycles per core Total Cycles Execution time per core (sec) Speedup Math IC per CPI for Math Cycles across Math IC LIS IC per core CPI for LS Cycles across L/WIC Branch IC per CPI for Branch Cycles across Branch IC Total Cycles Execution time of cores in parallel (sec) core core Speedup 7.1 2.7 SON # Cores 7.1 2.7 7.38E+07 3.69E+07 1.84E+07 9.22E+06 4.61E+06 6.6 6.6 6.6 6.6 6.6 4.87E+08 2.43E+08 1.22E+08 6.08E+07 3.04E+07 9.09E+07 4.54E+07 2.27E+07 1.14E+07 5.68E+06 7.1 7.1 7.1 6.45E+08 3.23E+08 1.61E+08 8.06E+07 4.03E+07 1.39E+08 6.96E+07 3.48E+07 1.74E+07 8.70E+06 2.7 2.7 2.7 3.76E+08 1.88E+08 9.40E+07 4.70E+07 2.35E+07 1.51E+09 7.54E+08 3.77E+08 1.88E+08 9.42E+07 0.4308 0.2154 0.1077 0.0539 0.0269 1.69 3.39 6.78 13.56 27.12 32 16 8 4 N # Cores Math IC per core 1.8 CPI for Math Math Cycles per core LIS IC per core 3.0 3.0 3.0 3.0 30 CPI for LS L/W Cycles per core Branch IC per core 6.9 6.9 6.9 6.9 6.9 CPI for Branch Branch Cycles per core Total Cycles Execution time per core (sec) Speedup

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts